3 mib block counters memory map, Mib block counters memory map -8 – Freescale Semiconductor MCF5480 User Manual

Page 938

MCF548x Reference Manual, Rev. 3

30-8

Freescale Semiconductor

30.3.3

MIB Block Counters Memory Map

defines the MIB Counters memory map which defines the locations in the MIB RAM space

where hardware maintained counters reside. These fall in the 0x9200–0x93FF address offset range for

FEC0 and the 0x9A00–0x9BFF address offset range for FEC1. The counters are divided into two groups.

RMON counters are included which cover the Ethernet statistics counters defined in RFC 1757. In addition

to the counters defined in the Ethernet statistics group, a counter is included to count truncated frames as

the FEC only supports frame lengths up to 2047 bytes. The RMON counters are implemented

independently for transmit and receive to insure accurate network statistics when operating in full duplex

mode.

IEEE counters are included which support the mandatory and recommended counter packages defined in

Section 5 of ANSI/IEEE Std. 802.3 (1998 edition). The IEEE Basic Package objects are supported by the

FEC but do not require counters in the MIB block. In addition, some of the recommended package objects

0x9128–

0x9140

0x9828–

0x9840

Reserved

0x9144

0x9944

FEC Transmit FIFO Watermark

FECTFWR

0x9184

0x9984

FEC Receive FIFO Data Register

FECRFDR

0x9188

0x9988

FEC Receive FIFO Status Register

FECRFSR

0x918C

0x998C

FEC Receive FIFO Control Register

FECRFCR

0x9190

0x9990

FEC Receive FIFO Last Read Frame Pointer

FECRLRFP

0x9194

0x9994

FEC Receive FIFO Last Write Frame Pointer

FECRLWFP

0x9198

0x9998

FEC Receive FIFO Alarm Register

FECRFAR

0x919C

0x999C

FEC Receive FIFO Read Pointer Register

FECRFRP

0x91A0

0x99A0

FEC Receive FIFO Write Pointer Register

FECRFWP

0x91A4

0x99A4

FEC Transmit FIFO Data Register

FECTFDR

0x91A8

0x99A8

FEC Transmit FIFO Status Register

FECTFSR

0x91AC

0x99AC

FEC Transmit FIFO Control Register

FECTFCR

0x91B0

0x99B0

FEC Transmit FIFO Last Read Frame Pointer

FECTLRFP

0x91B4

0x99B4

FEC Transmit FIFO Last Write Frame Pointer

FECTLWFP

0x91B8

0x99B8

FEC Transmit FIFO Alarm Register

FECTFAR

0x91BC

0x99BC

FEC Transmit FIFO Read Pointer Register

FECTFRP

0x91C0

0x99C0

FEC Transmit FIFO Write Pointer Register

FECTFWP

0x91C4

0x99C4

FIFO Reset Register

FECFRST

0x91C8

0x99C8

CRC and Transmit Frame Control Word Register

FECCTCWR

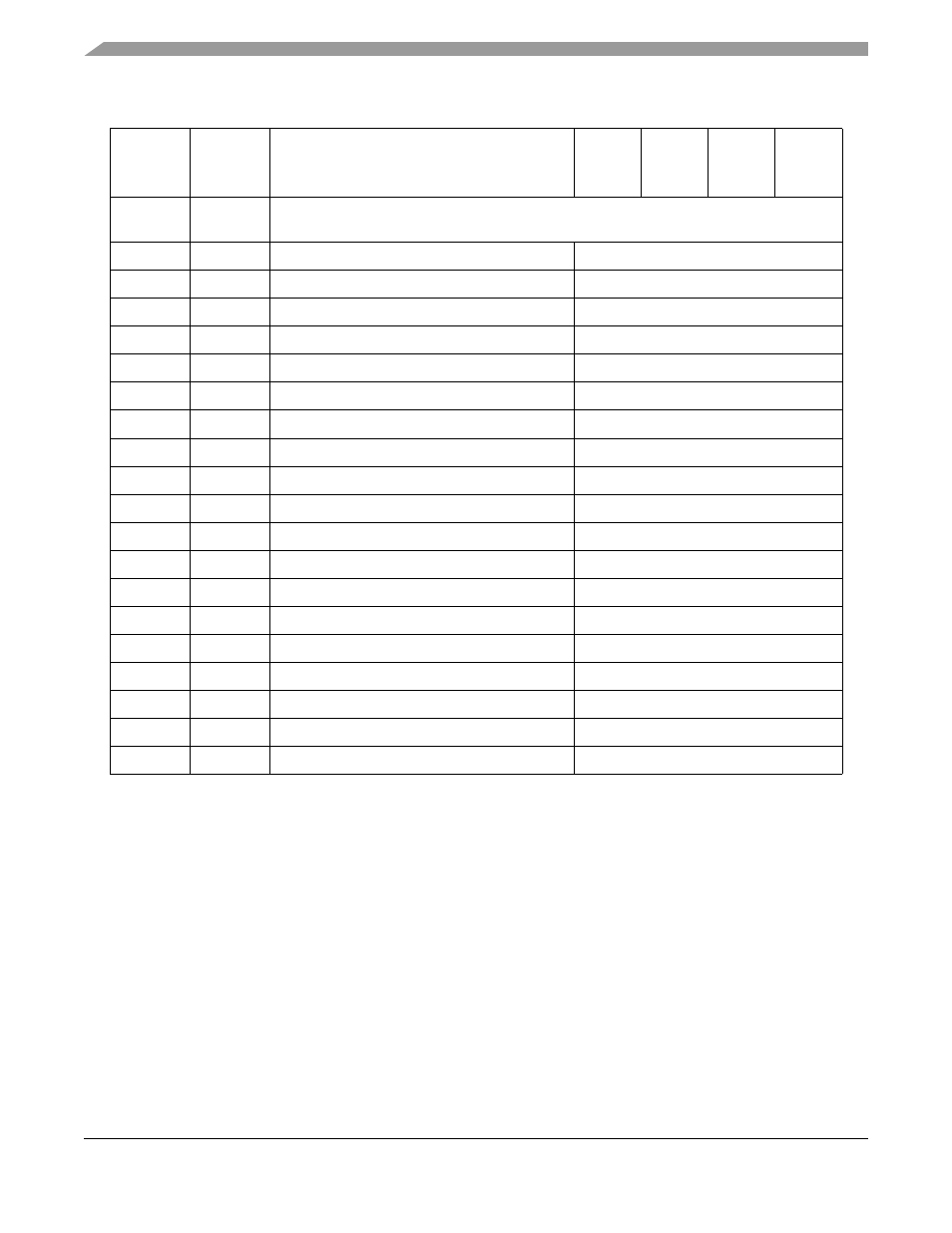

Table 30-5. FEC Register Memory Map (Continued)

MBAR

Offset for

FEC0

MBAR

Offset for

FEC1

Name

Byte 0

Byte 1

Byte 2

Byte 3