13 target ready (pcitrdy), 3 memory map/register definition, Target ready (pcitrdy) -4 – Freescale Semiconductor MCF5480 User Manual

Page 488: Memory map/register definition -4

MCF548x Reference Manual, Rev. 3

19-4

Freescale Semiconductor

19.2.13 Target Ready (PCITRDY)

The PCITRDY signal is asserted active low by the currently addressed target to indicate that it is ready to

complete the current data phase.

19.3

Memory Map/Register Definition

The MCF548x has several sets of registers that control and report status for the different interfaces to the

PCI controller: PCI Type 0 configuration space registers, general status/control registers, and

communication subsystem interface registers. All of these registers are accessible as offsets of MBAR. As

an XL bus master, an external PCI bus master can access MBAR space for register updates.

PCIRESET is controlled by a bit in the register space, PCIGSCR[PR], and must first be cleared before

external PCI devices wake-up. In other words, an external PCI master cannot load configuration software

across the PCI bus until this bit is cleared by software. Access to all internal registers is supported

regardless of the value held in PCIGSCR[PR].

All registers are accessible at an offset of MBAR in the memory space. There are two module offsets for

PCI configuration space. One is allocated to the communication subsystem interface registers and the other

to all other PCI controller registers including the standard Type 0 PCI configuration space. Software reads

from unimplemented registers return 0x00000000 and writes have no effect.

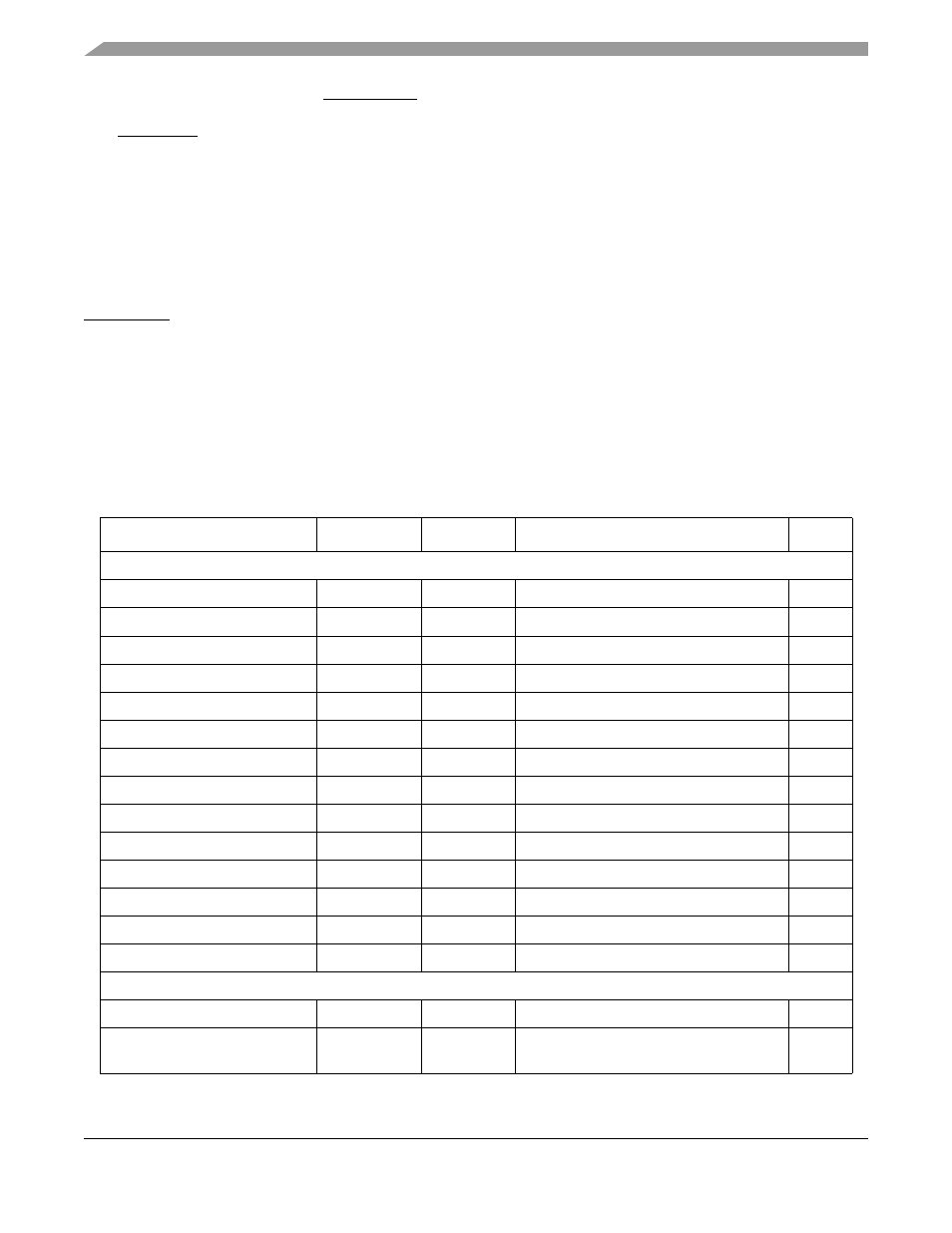

Table 19-2. PCI Memory Map

Address

Name

Size

Description

Access

PCI Type 0 Configuration Registers

MBAR + 0xB00

PCIIDR

32

PCI Device ID/Vendor ID

R

MBAR + 0xB04

PCISCR

32

PCI Status/Command

R/W

MBAR + 0xB08

PCICCRIR

32

PCI Class Code/Revision ID

R

MBAR + 0xB0C

PCICR1

32

PCI Configuration 1 Register

R/W

MBAR + 0xB10

PCIBAR0

32

PCI Base Address Register 0

R/W

MBAR + 0xB14

PCIBAR1

32

PCI Base Address Register 1

R/W

MBAR + 0xB18–0xB24

—

—

Reserved

—

MBAR + 0xB28

PCICCPR

32

PCI Cardbus CIS Pointer

R/W

MBAR + 0xB2C

PCISID

32

Subsystem ID/Subsystem Vendor ID

R/W

MBAR + 0xB30

PCIERBAR

32

PCI Expansion ROM

R/W

MBAR + 0xB34

PCICPR

32

PCI Capabilities Pointer

R/W

MBAR + 0xB38

—

—

Reserved

—

MBAR + 0xB3C

PCICR2

32

PCI Configuration Register 2

R/W

MBAR + 0xB40–0xB5C

—

—

Reserved

—

General Control/Status Registers

MBAR + 0xB60

PCIGSCR

32

Global Status/Control Register

R/W

MBAR + 0xB64

PCITBATR0

32

Target Base Address Translation Register

0

R/W