9 transmit control register (tcr), Transmit control register (tcr) -19 – Freescale Semiconductor MCF5480 User Manual

Page 949

Memory Map/Register Definition

MCF548x Reference Manual, Rev. 3

Freescale Semiconductor

30-19

30.3.3.9

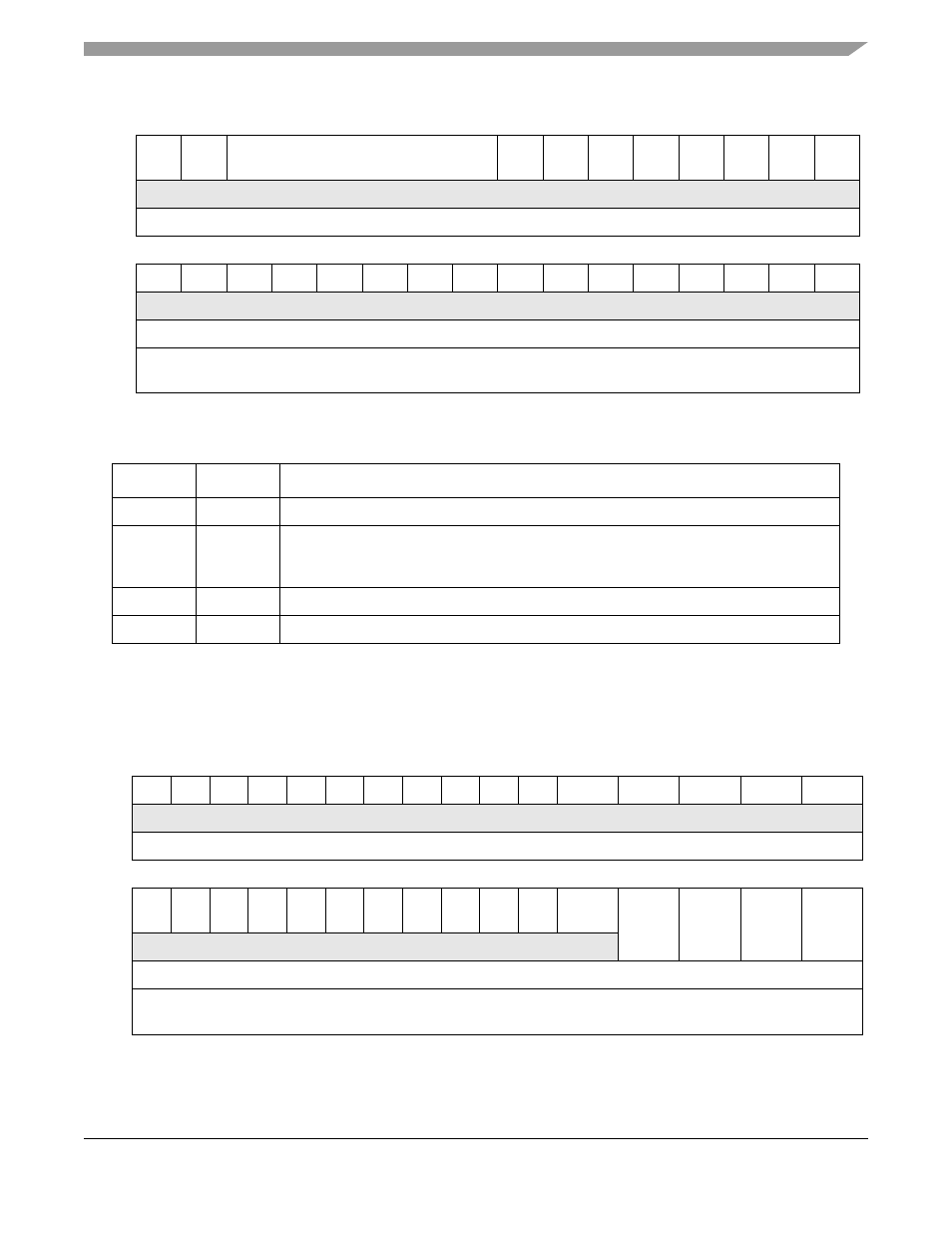

Transmit Control Register (TCR)

The TCR is read/write and is written by the user to configure the transmit block. This register is cleared at

system reset. Bits 2 and 1 should be modified only when ECR[ETHER_EN] is cleared.

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

R FCE

MULT

CAST

HASH

0

0

0

0

0

0

0

0

W

Reset

Uninitialized

0

0

0

0

0

0

0

0

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

R

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

W

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Reg

Addr

MBAR + 0x9088 (FEC0), 0x9888 (FEC1)

Figure 30-9. Receive Hash Register (RHR)

Table 30-15. RHR Bits Description

Bits

Name

Description

31

FCE

This is a read only view of the flow control enable (FCE) bit in the RCR.

30

MULTCAST Set if the current receive frame contained a multi-cast destination address (the least

significant bit of the DA was set). Cleared if the current receive frame does not correspond

to a multi-cast address.

29–24

HASH

Corresponds to the “hash” value of the current receive frame’s destination address.

23–0

—

Reserved, should be cleared.

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

R

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

W

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

R

0

0

0

0

0

0

0

0

0

0

0

RFC_

PAUSE

TFC_

PAUSE

FDEN

HBC

GTS

W

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Reg

Addr

MBAR + 0x90C4 (FEC0), 0x98C4 (FEC1)

Figure 30-10. Transmit Control Register (TCR)