10 pc breakpoint asid register (pbasid), Pc breakpoint asid register (pbasid) -24 – Freescale Semiconductor MCF5480 User Manual

Page 274

MCF548x Reference Manual, Rev. 3

8-24

Freescale Semiconductor

DBRs support both aligned and misaligned references.

shows relationships between processor

address, access size, and location within the 32-bit data bus.

8.4.10

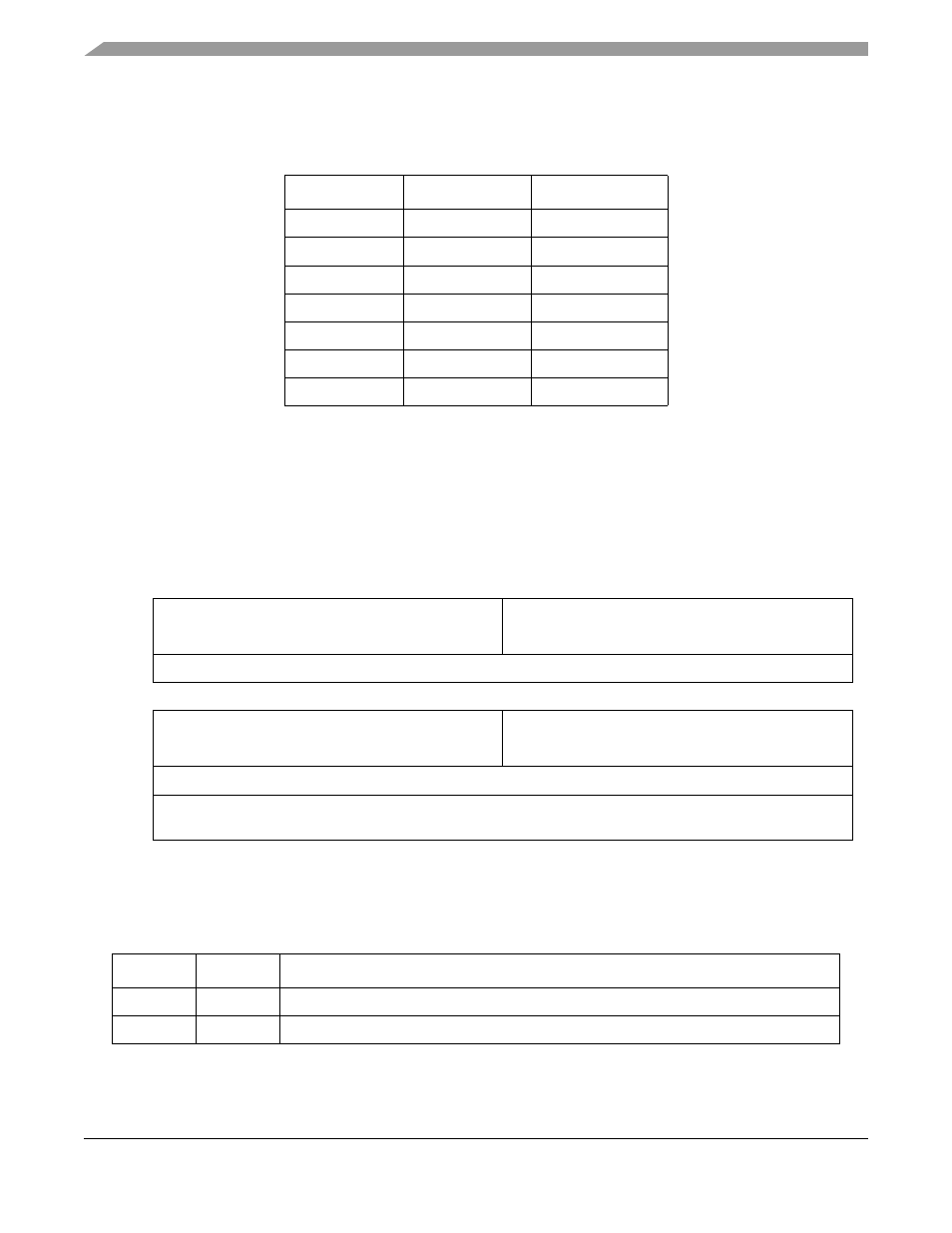

PC Breakpoint ASID Register (PBASID)

Each PC breakpoint register (PBR, PBR1, PBR2, or PBR3) specifies an instruction address that can be

used to trigger a breakpoint. To support debugging in a virtual environment, an ASID can optionally be

associated with the instruction address in the PC breakpoint registers. The optional specification of an

ASID value is made using PBASID and its exact inclusion within the breakpoint specification defined by

the PBAC.

PBASID contains one 8-bit ASID values for each PC breakpoint register, as described in

,

which allows each PC breakpoint register to be associated with a unique virtual address and process.

Table 8-19. Access Size and Operand Data Location

A[1:0]

Access Size

Operand Location

00

Byte

D[31:24]

01

Byte

D[23:16]

10

Byte

D[15:8]

11

Byte

D[7:0]

0x

Word

D[31:16]

1x

Word

D[15:0]

xx

Longword

D[31:0]

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

R

PBR3ASID

PBR2ASID

W

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

R

PBR1ASID

PBRASID

W

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Reg

Addr

CPU + 0x14

Figure 8-16. PC Breakpoint ASID Register (PBASID)

Table 8-20. PBASID Field Descriptions

Bits

Name

Description

31–24

PBA3SID

PBR3ASID. Corresponds to the ASID associated with PBR3.

23–16

PBA2SID

PBR2ASID Corresponds to the ASID associated with PBR2.