Freescale Semiconductor MCF5480 User Manual

Page 491

Memory Map/Register Definition

MCF548x Reference Manual, Rev. 3

Freescale Semiconductor

19-7

19.3.1.1

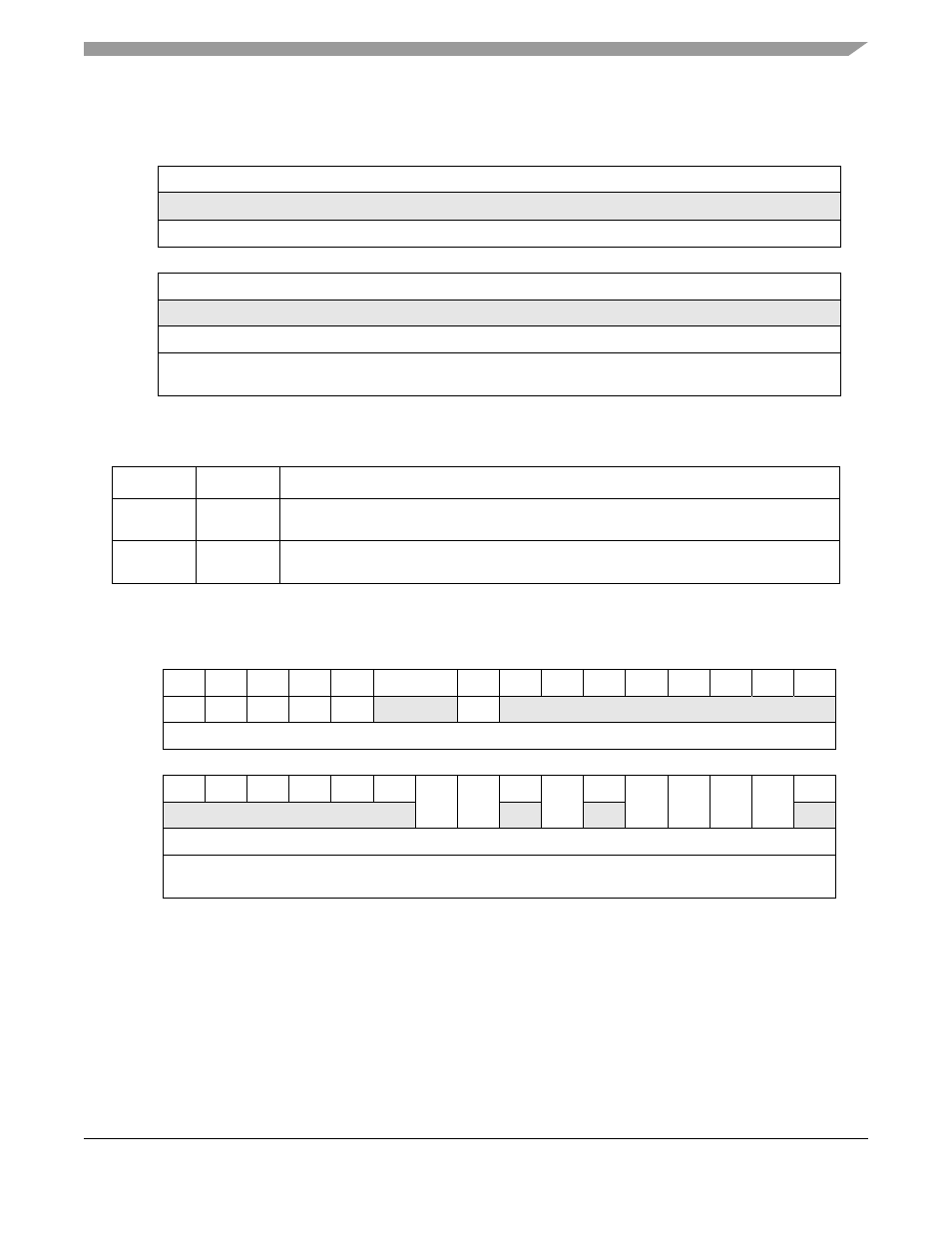

Device ID/Vendor ID Register (PCIIDR)—PCI Dword Addr 0

19.3.1.2

PCI Status/Command Register (PCISCR)—PCI Dword Addr 1

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

R

Device ID

W

Reset

0

1

0

1

1

0

0

0

0

0

0

0

0

1

1

0

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

R

Vendor ID

W

Reset

0

0

0

1

0

0

0

0

0

1

0

1

0

1

1

1

Reg

Addr

MBAR + 0xB00

Figure 19-2. Device ID/Vendor ID Register (PCIIDR)

Table 19-3. PCIIDR Field Descriptions

Bits

Name

Description

31–16

Device ID

This field is read-only and represents the PCI Device Id assigned to the MCF548x. Its

value is: 0x5806.

15–0

Vendor ID

This field is read-only and represents the PCI Vendor Id assigned to the MCF548x. Its

value is: 0x1057.

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

R

PE

SE

MA

TR

TS

DT

DP

FC

R

66M

C

0

0

0

0

W rwc

1

rwc

1

rwc

1

rwc

1

rwc

1

rwc

1

Reset

0

0

0

0

0

0

1

0

1

0

1

0

0

0

0

0

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

R

0

0

0

0

0

0

F

S

ST

PER

V

MW

SP

B

M

IO

W

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Reg

Addr

MBAR + 0xB04

1

Bits 31-27 and 24 are read-write-clear (rwc).

—Hardware can set rwc bits, but cannot clear them.

—Only PCI configuration cycles can clear rwc bits that are currently set by writing a 1 to the bit location.

Writing a 1 to a rwc bit that is currently a 0 or writing a 0 to any rwc bit has no effect.

Figure 19-3. PCI Status/Command Register (PCISCR)