6 mir mode, Mir mode -53 – Freescale Semiconductor MCF5480 User Manual

Page 815

Software Environment

MCF548x Reference Manual, Rev. 3

Freescale Semiconductor

26-53

26.7.2.6

MIR Mode

Applying clock to the PSCBCLK input and programming the control registers are required to initialize in

MIR mode. Here is a sample sequence when the input frequency of PSCBCLK is 18.432 MHz. (1.152

MHz x 16).

8

PSCMR2

07

CM[1:0]=00

Normal mode (not test mode)

TxRTS=0

PSCnRTS is not controlled by transmitter

TxCTS=0

PSCnCTS does not control transmitter

SB[3:0]=0111

1 stop bit

9

PSCIRCR1

00

FD=0

Receiver is disabled while transmitting

SPUL=1

Pulse width is 1.6 us

10

PSCIRSTR

36

IRSTIM=54 (dec)

Counter value for 1.6 us pulse

11

PSCRFCR

0F

WRITE TAG = 00

Not EOF

FRMEN=1

Enable frame mode

GR[2:0]=100

Granularity is 4 byte

12

PSCTFCR

0F

WRITE TAG = 00

Not EOF

FRMEN=1

Enable frame mode

GR[2:0]=100

Granularity is 16 byte

13

PSCRFAR

00F0

ALARM[8:0]=0F0

Request is asserted if # of data >= 240

14

PSCTFAR

00F0

ALARM[8:0]=0F0

Request is asserted if # of empty >= 240

15

PSCCR

04

TC=01

Enable transmitter

RC=00

Receiver remains at disabled state.

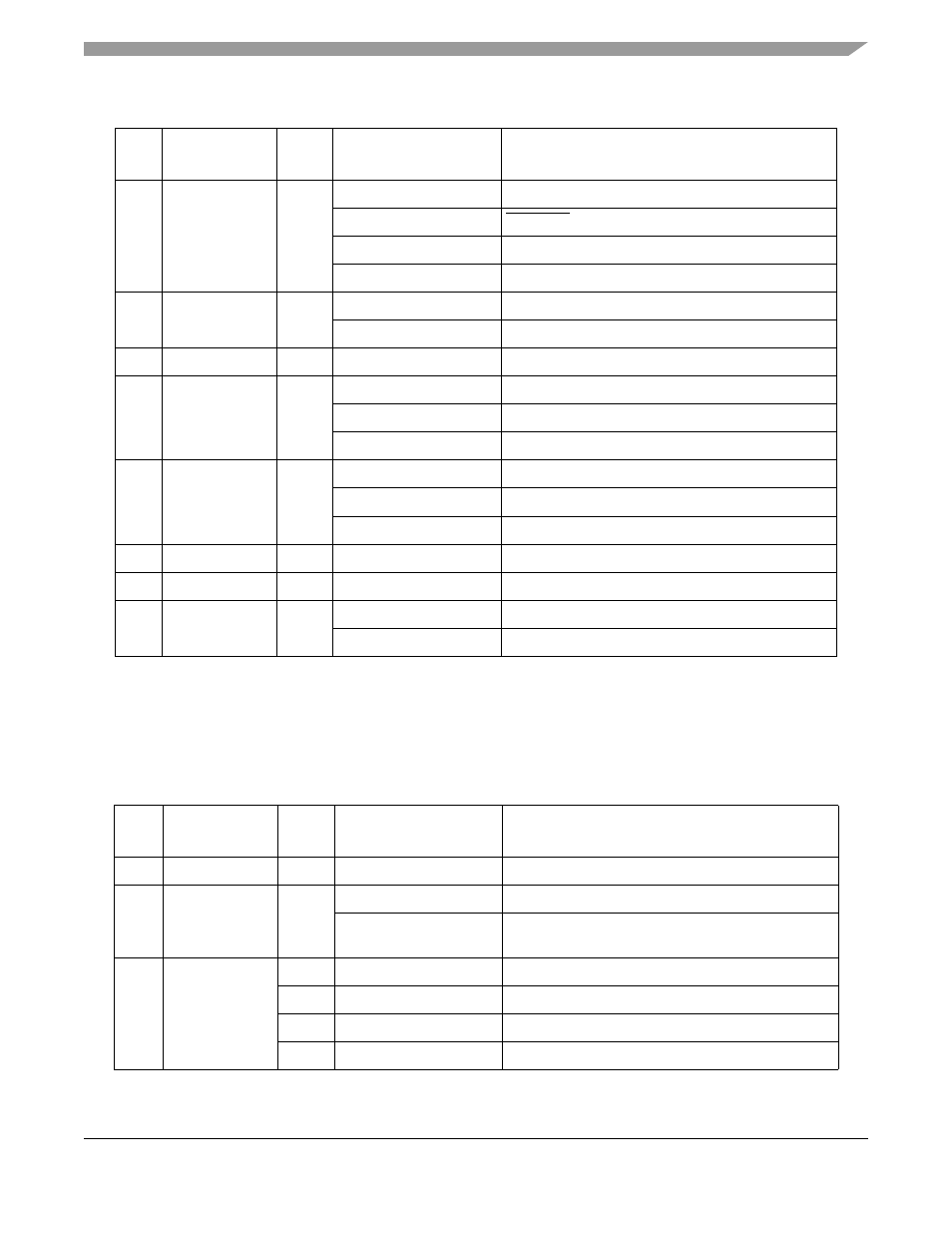

Table 26-45. A Sample Initialization Sequence for MIR Mode

Step

No.

Register

Value

Details

Meaning

1

PSCSICR

05

SIM[2:0]=101

MIR mode

2

PSCIRMFD

0F

FREQL=0

1.152 Mbps mode

M_FDIV[4:0]=01111

Frequency divide ratio is 16.

So f(PSCBCLK) should be 18.432 MHz.

3

PSCCR

20

MISC=010

Reset receiver and RxFIFO

30

MISC=011

Reset transmitter and TxFIFO

40

MISC=100

Reset all error status

10

MISC=001

Reset MR pointer

Table 26-44. A Sample Initialization Sequence for SIR Mode (Continued)

Step

No.

Register

Value

Details

Meaning