Freescale Semiconductor MCF5480 User Manual

Page 49

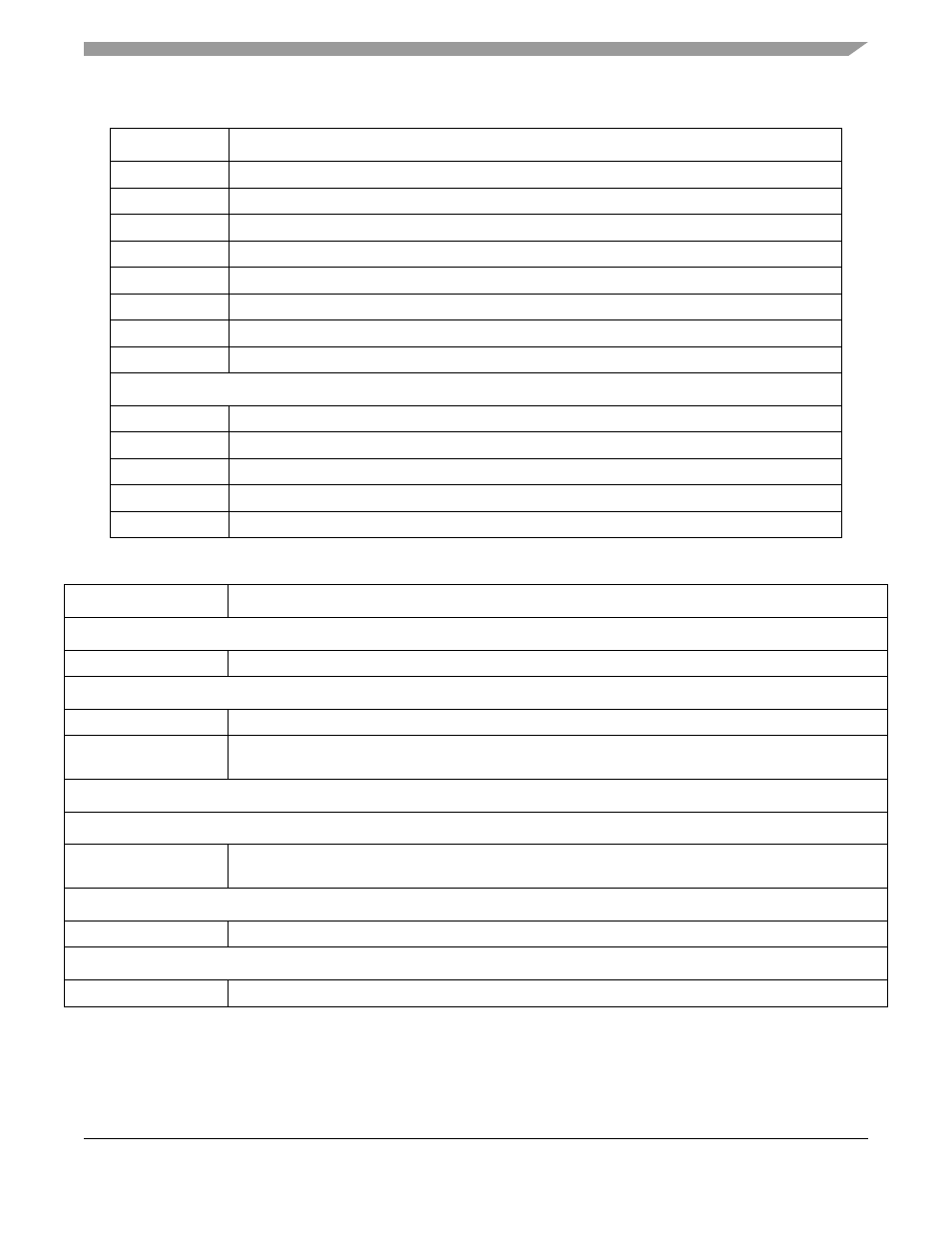

Terminology and Notational Conventions

MCF548x Reference Manual, Rev. 3

Freescale Semiconductor

xlix

Address

Calculated effective address (pointer)

Bit

Bit selection (example: Bit 3 of D0)

lsb

Least significant bit (example: lsb of D0)

LSB

Least significant byte

LSW

Least significant word

msb

Most significant bit

Most significant byte

MSW

Most significant word

Condition Code Register Bit Names

C

Carry

N

Negative

V

Overflow

X

Extend

Z

Zero

Table iv. MCF548x Revision History

Section/Page

Substantive Changes

Revision 1.0 (03/2004)

Initial release.

Revision 1.1 (03/2004

Changed instances of FEC2 to FEC1 and FEC1 to FEC0.

Changed instances of FEC2 to FEC1 and FEC1 to FEC0.

Revision 1.2 (03/2004)

Revision 2.0 (10/2004)

Many content changes, the biggest being greatly enhancing the MC-DMA chapter and adding Clocks and

Internal Buses chapter. Many editorial changes.

Revision 2.1 (10/2004)

Chapter 17

Took out FlexCan chapter. Fixed timing diagrams in FlexBus chapter.

Revision 3.0 (01/2006)

Throughout

Added all documentation errata from Revision 3 of the MCF5485RMAD document as described below.

Table iii. Notational Conventions (continued)

Instruction

Operand Syntax