2 mmu memory map, 3 mmu control register (mmucr), Mmu memory map -11 – Freescale Semiconductor MCF5480 User Manual

Page 177: Mmu control regist, Table 5-3, Describes mmu base address register fields

MMU Definition

MCF548x Reference Manual, Rev. 3

Freescale Semiconductor

5-11

5.5.3.2

MMU Memory Map

MMUBAR holds the base address for the 64-Kbyte MMU memory map, shown in

memory map area is not visible unless the MMUBAR is valid and must be referenced aligned. A large

portion of the map is reserved for future use.

The address space ID (ASID) is located in a CPU space control register. The 8-bit ASID value located in

the low order byte of a 32-bit supervisor control register, mapped into CPU space at address 0x003 and

accessed using a MOVEC instruction. The ColdFire Family Programmer’s Reference Manual describes

MOVEC.

This 8-bit field is the current user ASID. The ASID is an extension to the virtual address. Address space

0x00 may be reserved for supervisor mode. See address space mode functionality in

.” The other 255 address spaces are used to tag user processes. The

TLB entry ASID values are compared to this value for user mode unless the TLB entry is marked shared

(MMUTR[SG] is set). The TLB entry ASID value may be compared to 0x00 for supervisor accesses.

5.5.3.3

MMU Control Register (MMUCR)

MMUCR,

, has the address space mode and virtual mode enable bits. The user must force

pipeline synchronization after writing to this register. Therefore, all writes to this register must be

immediately followed by a NOP instruction.

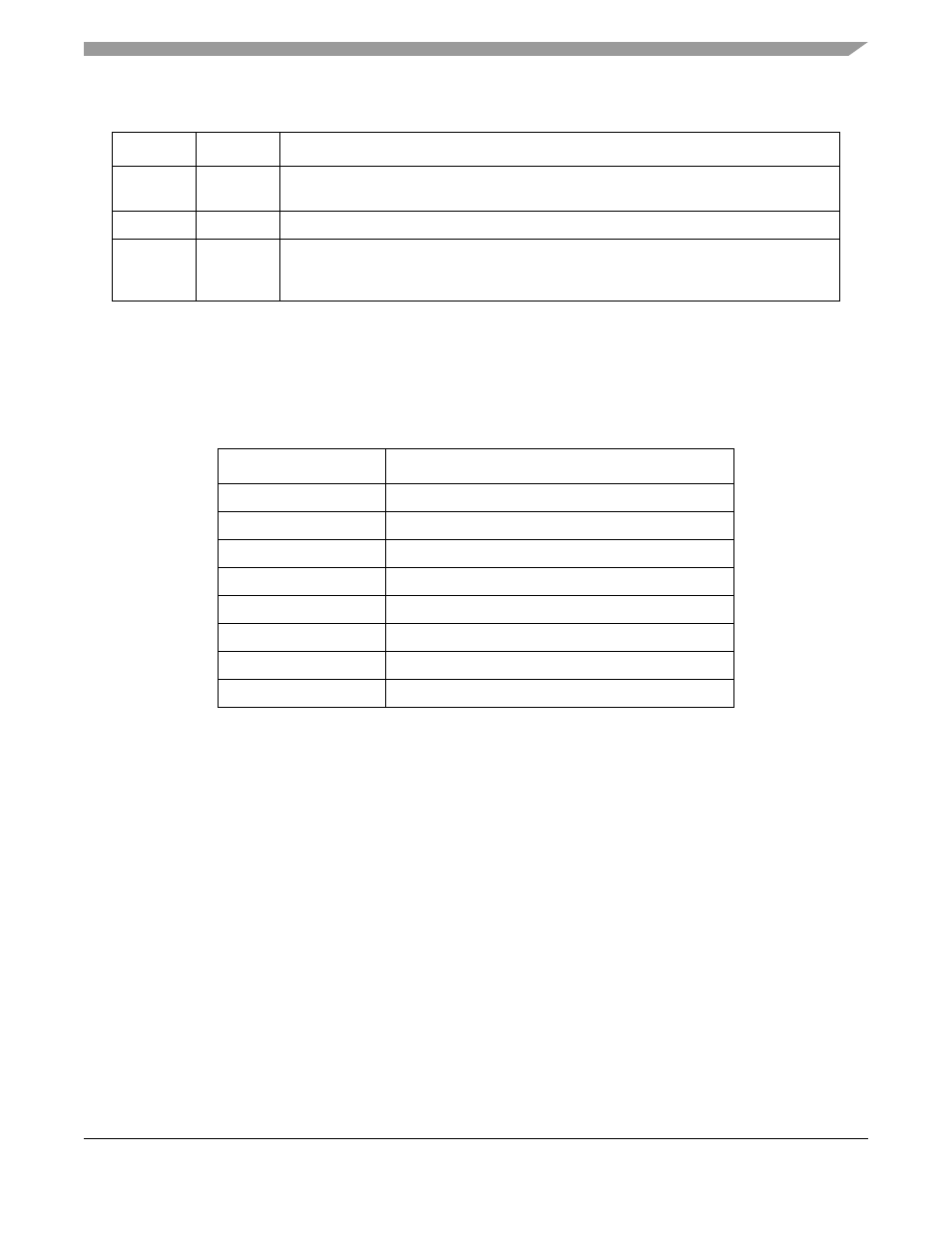

Table 5-3. MMUBAR Field Descriptions

Bits

Name

Description

31–16

BA

Base address. Defines the base address for the 64-Kbyte address space mapped to the

MMU.

15–1

—

Reserved, should be cleared. Writes are ignored and reads return zeros.

0

V

Valid. Indicates when MMUMBAR contents are valid. BA is not used unless V is set.

0 MMUBAR contents are not valid.

1 MMUBAR contents are valid.

Table 5-4. MMU Memory Map

Offset from MMUBAR

Name

+ 0x0000

MMU control register (MMUCR)

+ 0x0004

MMU operation register (MMUOR)

+ 0x0008

MMU status register (MMUSR)

+ 0x000C

Reserved

+ 0x0010

MMU fault, test, or TLB address register (MMUAR)

+ 0x0014

MMU read/write TLB tag register (MMUTR)

+ 0x0018

MMU read/write TLB data register (MMUDR)

+ 0x001C–0xFFFC

Reserved

1

May be used for implementation-specific information/control registers