Freescale Semiconductor MCF5480 User Manual

Page 824

MCF548x Reference Manual, Rev. 3

27-6

Freescale Semiconductor

25

PCSSE

Peripheral chip select strobe enable. Selects between the DSPICS5 and PCSS functions. See

Section 27.7.3.5, “Peripheral Chip Select Strobe Enable (PCSS)

” for more information.

0 DSPICS5/PCSS is used as the DSPICS5 signal

1 DSPICS5/PCSS is used as PCSS peripheral strobe signal

24

ROOE

Receive FIFO overflow overwrite enable. Enables an Rx FIFO overflow condition to either ignore

the incoming serial data or to overwrite existing data. If the Rx FIFO is full and new data is received,

the data from the transfer that generated the overflow is either ignored or shifted into the shift

register. If the ROOE bit is set, the incoming data is shifted into the shift register. If the ROOE bit is

cleared, the incoming data is ignored. See

Section 27.7.6.6, “Receive FIFO Overflow Interrupt

” for more information.

0 Incoming data is ignored

1 Incoming data is shifted into the shift register

23–22,

20, 17

—

Reserved, should be cleared.

21,19–18,1

6

CSISn

Chip select inactive state. Determines the inactive state of the DSPICSn signal.

0 The inactive state of DSPICSn is low

1 The inactive state of DSPICSn is high

15–14

—

Reserved, should be cleared.

13

DTXF

Disable transmit FIFO. Provides a mechanism to disable the Tx FIFO. When the Tx FIFO is

disabled, the transmit part of the DSPI operates as a simplified double-buffered SPI. See

Section 27.7.2.3, “FIFO Disable Operation

” for details.

0 Tx FIFO is enabled

1 Tx FIFO is disabled

12

DRXF

Disable receive FIFO. Provides a mechanism to disable the Rx FIFO. When the Rx FIFO is

disabled, the receive part of the DSPI operates as a simplified double-buffered SPI. See

Section 27.7.2.3, “FIFO Disable Operation

” for details.

0 Rx FIFO is enabled

1 Rx FIFO is disabled

11

CTXF

Clear transmit FIFO. CTXF is used to flush the Tx FIFO. Writing a ‘1’ to CTXF clears the Tx FIFO

counter. The CTXF bit is always read as zero.

0 Do not clear the Tx FIFO

1 Clear the Tx FIFO counter

10

CRXF

Clear receive FIFO. CRXF is used to flush the Rx FIFO. Writing a ‘1’ to CRXF clears the Rx FIFO

counter. The CRXF bit is always read as zero.

0 Do not clear the Rx FIFO

1 Clear the Rx FIFO counter

9–8

SMPL_PT Sample point. Allows the host software to select when the DSPI master samples DSPISIN in

modified transfer format.

shows where the master can sample the DSPISIN pin.

00 0 system clocks between DSPISCK edge and DSPISIN sample

01 1 system clock between DSPISCK edge and DSPISIN sample

10 2 system clocks between DSPISCK edge and DSPISIN sample

11 Reserved

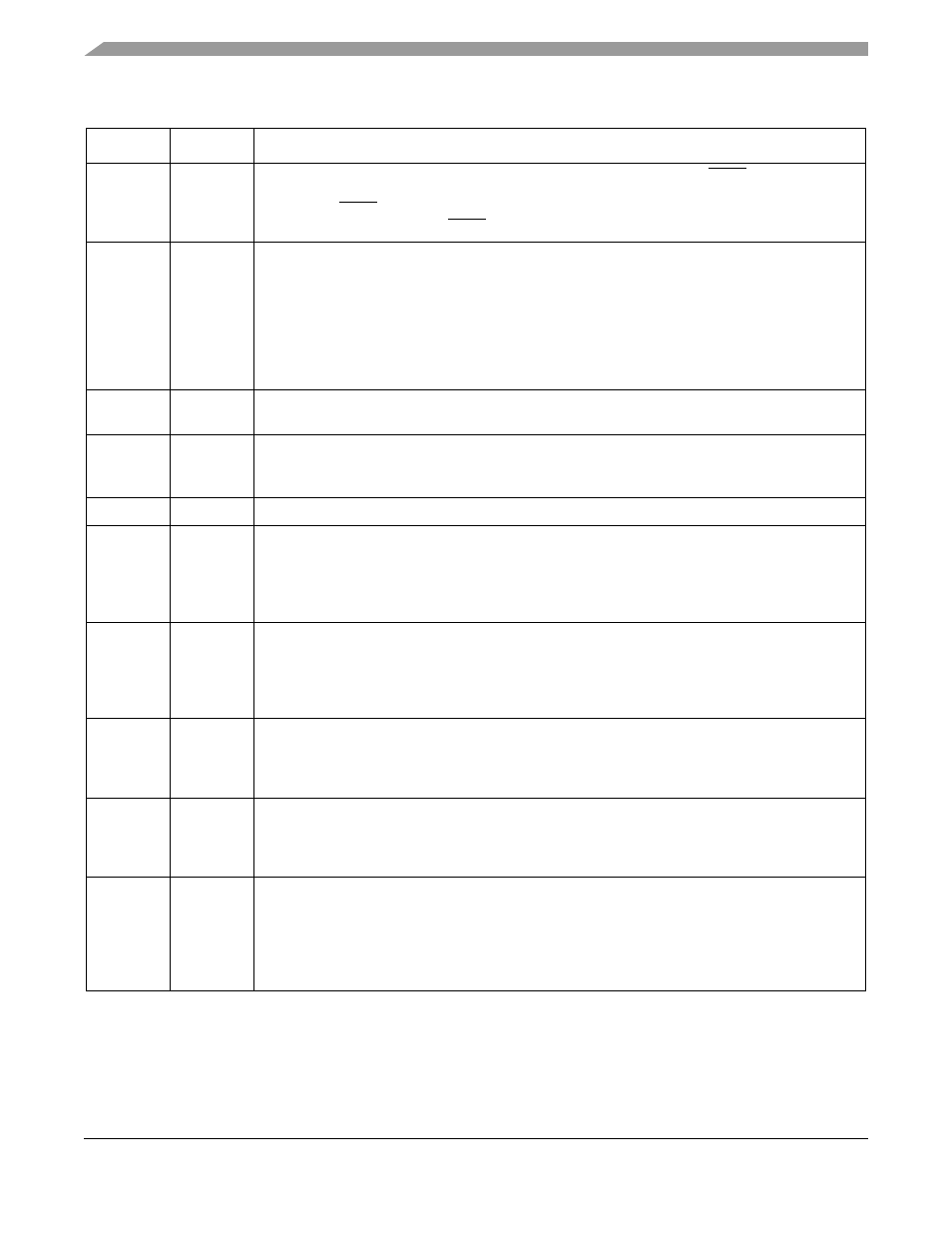

Table 27-3. DMCR Field Descriptions (Continued)

Bits

Name

Description