9 initiator control register (pciicr), Initiator control register (pciicr) -20 – Freescale Semiconductor MCF5480 User Manual

Page 504

MCF548x Reference Manual, Rev. 3

19-20

Freescale Semiconductor

19.3.2.9

Initiator Control Register (PCIICR)

Table 19-15.

PCIIWCR Field Descriptions

Bits

Name

Description

31–28

—

Reserved, should be cleared.

27–24

Window 0

Control[3:0]

Bit[3]—IO/M#.

0 Window is mapped to PCI memory.

1 Window is mapped to PCI I/O.

Bit[2:1]—PCI read command (PRC).

If bit[3] is programmed memory, “0”, then these bits are used to determine the type of PCI memory

command to issue. See

. If bit[3] is set to “1”, the value of these bits is meaningless.

00 PCI Memory Read.

01 PCI Memory Read Line.

10 PCI Memory Read Multiple.

11 Reserved.

Bit[0]—Enable.

This bit is set to indicate the address registers that control the XL bus initiator interface access to

PCI initialized and will be used. The PCI Controller can begin to decode XL bus PCI accesses.

0 Do not decode XL bus PCI accesses to Window.

1 Registers initialized—decode accesses to Window.

23–20

—

Reserved, should be cleared.

19–16

Window 1

Control[3:0]

Bit[3]—IO/M#.

Bit[2:1]—PRC.

Bit[0]—Enable.

15–12

Reserved

Reserved register. Write a zero to this register.

11–8

Window 2

Control[3:0]

Bit[3]—IO/M#.

Bit[2:1]—PRC.

Bit[0]—Enable.

7–0

—

Reserved, should be cleared.

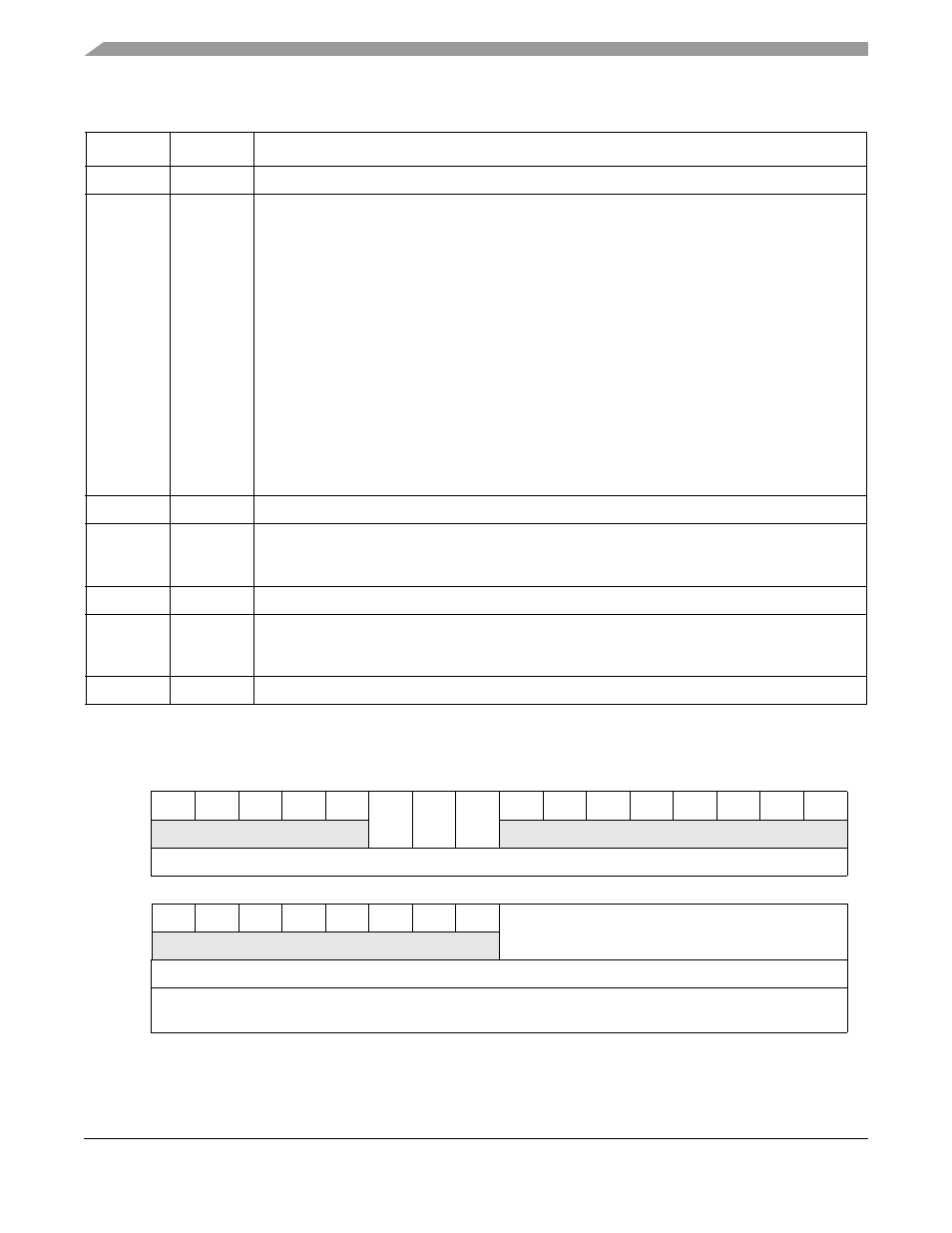

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

R

0

0

0

0

0

REE

IAE

TAE

0

0

0

0

0

0

0

0

W

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

R

0

0

0

0

0

0

0

0

Maximum Retries

W

Reset

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

Reg

Addr

MBAR + 0xB84

Figure 19-17. Initiator Control Register (PCIICR)