11 configuration address register (pcicar), Configuration address register (pcicar) -22 – Freescale Semiconductor MCF5480 User Manual

Page 506

MCF548x Reference Manual, Rev. 3

19-22

Freescale Semiconductor

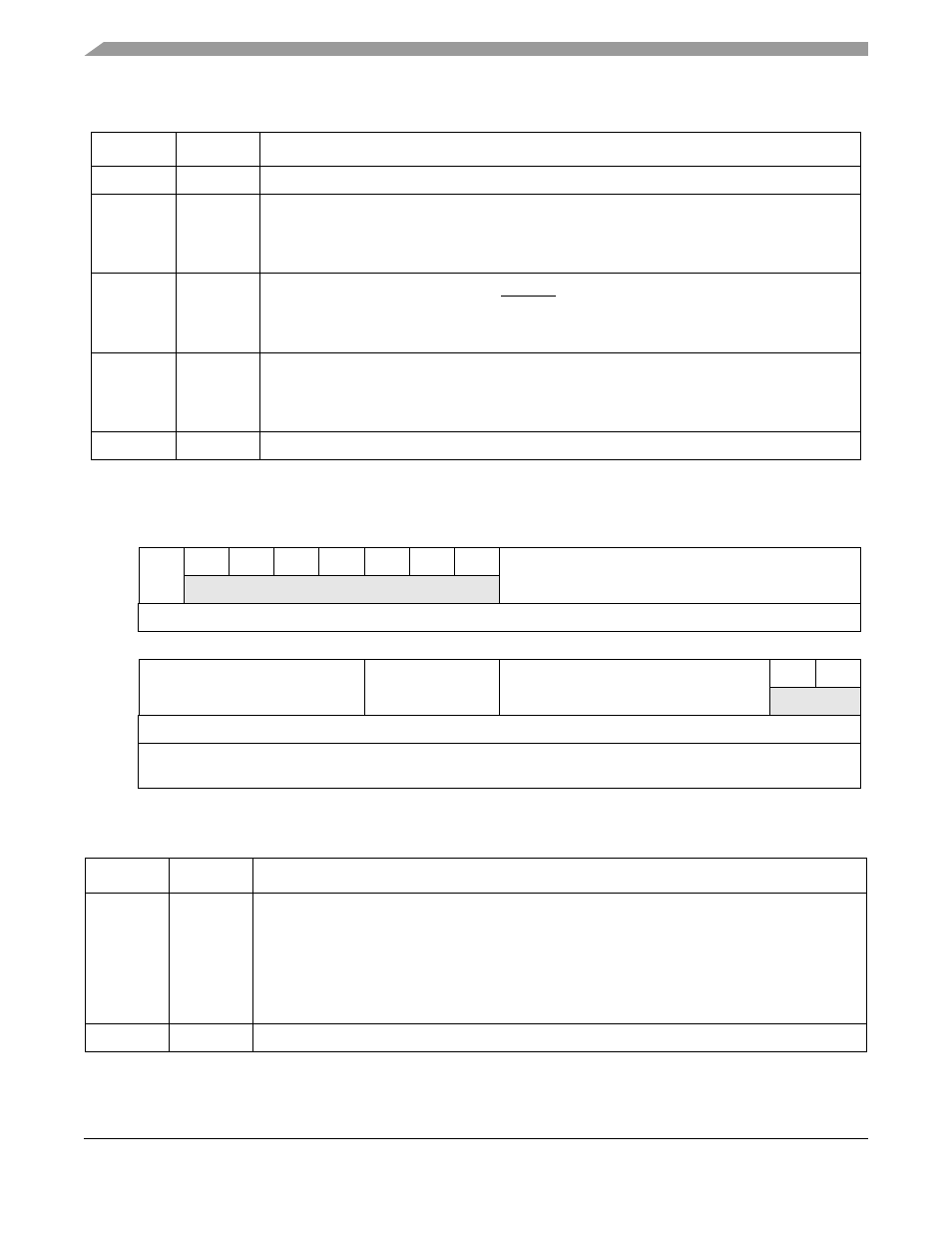

19.3.2.11 Configuration Address Register (PCICAR)

Table 19-17. PCIISR Field Descriptions

Bits

Name

Description

31–27

—

Reserved, should be cleared.

26

RE

Retry error. This flag is set when the controller ARTRY’s a read on XL bus when retry-terminated

by the PCI target or when the Max_Retries limit is reached for a single XL bus write transaction.

A CPU interrupt will be generated if PCIICR[RE] bit is set. It is up to application software to clear

this bit by writing ‘1’ to it.

25

IA

Initiator abort. This flag bit is set if the PCI controller issues an Initiator Abort flag. This indicates

that no Target responded by asserting DEVSEL within the time allowed for subtractive decoding.

A CPU interrupt will be generated if the PCIICR[IAE] bit is set. It is up to application software to

clear this bit by writing ‘1’ to it.

24

TA

Target abort. This flag bit is set if the addressed PCI Target has signalled an Abort. A CPU

interrupt will be generated if the PCIICR[TAE] bit is set. It is up to application software to query

the Target’s status register and determine the source of the error. It is up to application software

to clear this bit by writing ‘1’ to it.

23–0

—

Reserved, should be cleared.

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

R

E

0

0

0

0

0

0

0

Bus Number

W

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

R

Device Number

Function Number

DWORD

0

0

W

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Reg

Addr

MBAR + 0xBF8

Figure 19-19. Configuration Address Register (PCICAR)

Table 19-18.

PCICAR Field Descriptions

Bits

Name

Description

31

E

Enable. The enable flag that controls configuration space mapping. When enabled, subsequent

access to initiator window space defined as I/O in the PCIIWCR is translated into a PCI

configuration, special cycle, or interrupt acknowledge access using the configuration address

register information (

Section 19.4.4.2, “Configuration Mechanism”

). When disabled, a read or write

to the window is passed through to the PCI bus as an I/O transaction.

0 Disabled

1 Enabled

30–24

—

Reserved, should be cleared.