4 mdeu interrupt status register (mdisr), Mdeu interrupt status register (mdisr) -43, P. 22-43 – Freescale Semiconductor MCF5480 User Manual

Page 645

Message Digest Execution Unit (MDEU)

MCF548x Reference Manual, Rev. 3

Freescale Semiconductor

22-43

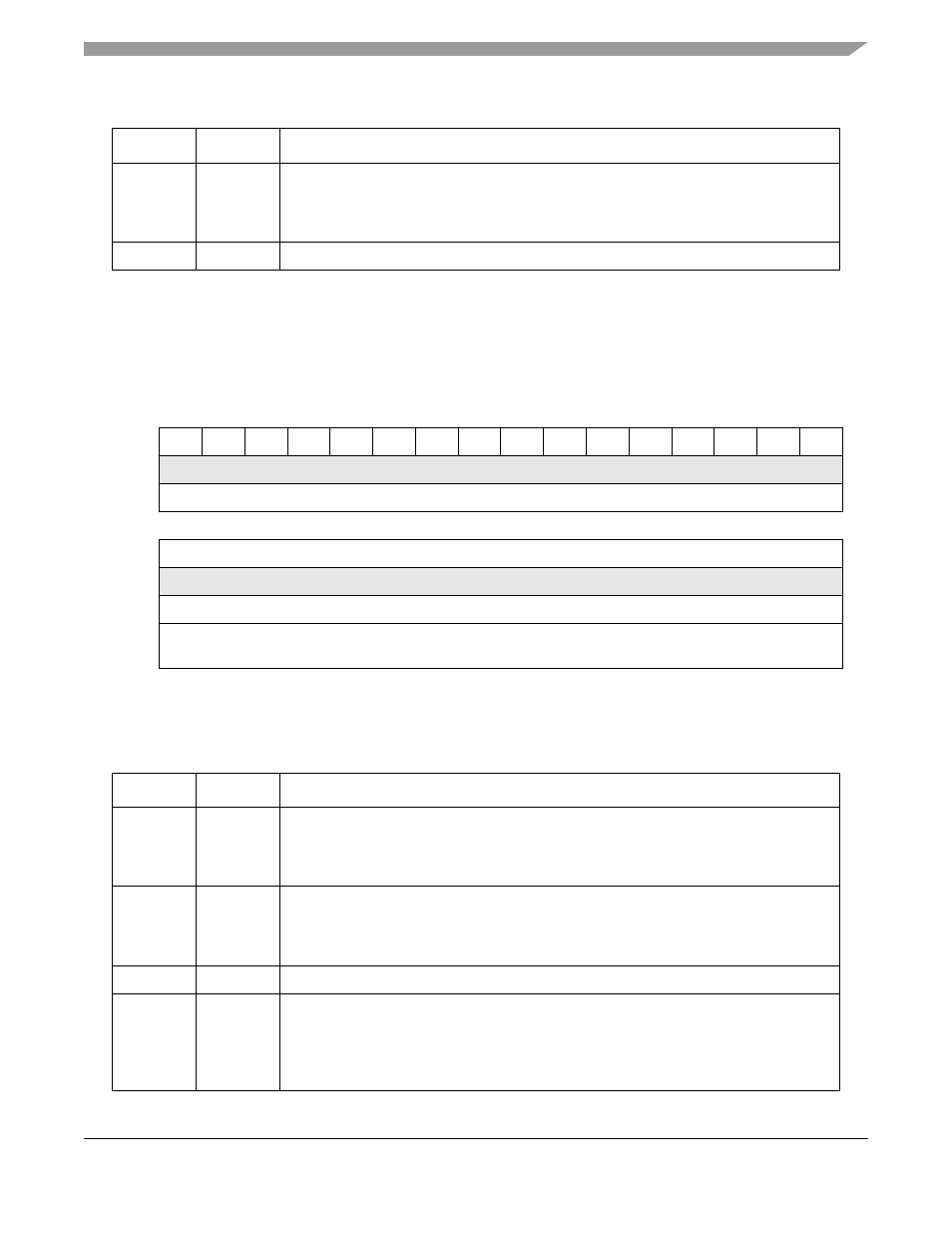

22.10.4 MDEU Interrupt Status Register (MDISR)

The interrupt status register tracks the state of possible errors, if those errors are not masked, via the

MDEU interrupt mask register. The definition of each bit in the interrupt status register is shown in

.

Figure 22-31. MDEU Interrupt Status Register (MDISR)

describes MDEU interrupt status register fields.

24

RD

Reset Done. This status bit, when high, indicates that MDEU has completed its reset

sequence, as reflected in the signal sampled by the appropriate crypto-channel.

0 Reset in progress

1 Reset done

23-0

—

Reserved, should be cleared.

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

R

ME

AE

0

0

0

IFO

0

0

0

0

0

IE

ERE

CE

KSE

DSE

W

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

R

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

W

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Reg

Addr

MBAR + 0x 21038

Table 22-28. MDISR Field Descriptions

Bits

Name

Description

31

ME

Mode Error. An illegal value was detected in the mode register. Note: writing to reserved

bits in mode register is likely source of error.

0 No error detected

1 Mode error

30

AE

Address Error. An illegal read or write address was detected within the MDEU address

space.

0 No error detected

1 Address Error

29–27

—

Reserved, should be cleared.

26

IFO

Input FIFO Overflow. The MDEU Input FIFO has been pushed while full.

0 No overflow detected

1 Input FIFO has overflowed

Note: When operating as a master, the implements flow-control, and FIFO size is not a

limit to data input.

Table 22-27. MDSR Field Descriptions (Continued)

Bits

Name

Description