Freescale Semiconductor MCF5480 User Manual

Page 51

Terminology and Notational Conventions

MCF548x Reference Manual, Rev. 3

Freescale Semiconductor

li

Add the following after Table 2-4:

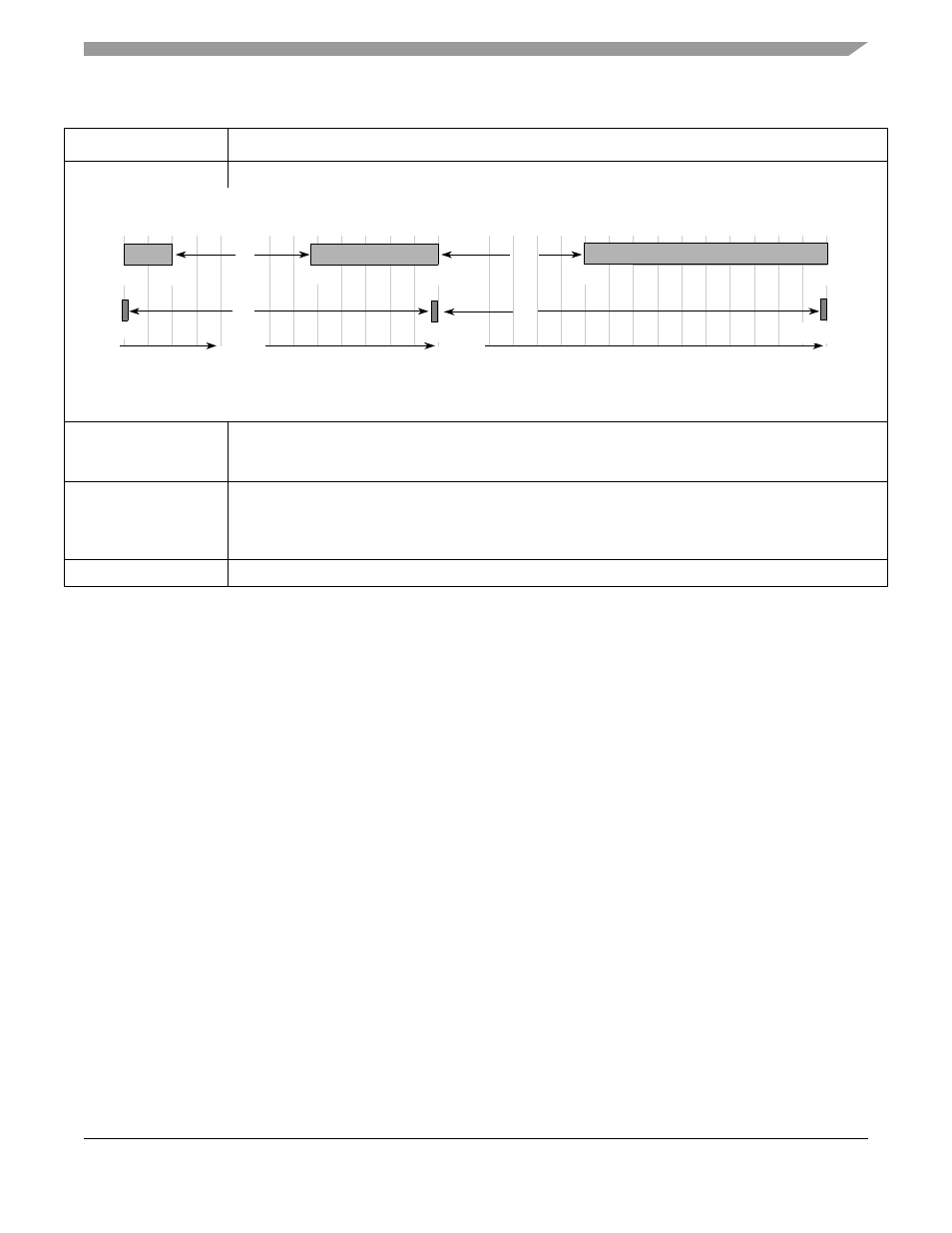

correlates CLKIN, internal bus, and core clock frequencies for the 1x–4x multipliers.

Figure 1. CLKIN, Internal Bus, and Core Clock Ratios

Change the second sentence of the first paragraph from “The second holds the 32-bit program counter

address of the faulted instruction.“ to “The second holds the 32-bit program counter address of the faulted

or interrupted instruction.”

The “Interrupt exception” entry’s description is outdated. Change from “Interrupt exception processing, with

interrupt recognition and vector fetching, includes uninitialized and spurious interrupts as well as those

where the requesting device supplies the 8-bit interrupt vector. Autovectoring can optionally be configured

through the system interface module (SIM).” to “Please refer to Chapter 13 ‘Interrupt Controller.’”

Add missing table using

from this document.

Table iv. MCF548x Revision History (continued)

Section/Page

Substantive Changes

25 40 50 60 70

70 80 90 100 110 120 130 140 150 160 170 180 190 200

60

25.0

50.0

100.0

CLKIN (MHz)

Core Clock (MHz)

Core Clock

CLKIN

200.0

40 50 60 70 80 90 100

30

50.0

100.0

Internal Clock

Internal Clock (MHz)

2x

2x

25.0

200.0

2x

4x

100.0