1 system breakpoint control register (sbcr), System breakpoint control register (sbcr) -3, Figure 9-1 – Freescale Semiconductor MCF5480 User Manual

Page 319

Memory Map/Register Definition

MCF548x Reference Manual, Rev. 3

Freescale Semiconductor

9-3

9.3.1.1

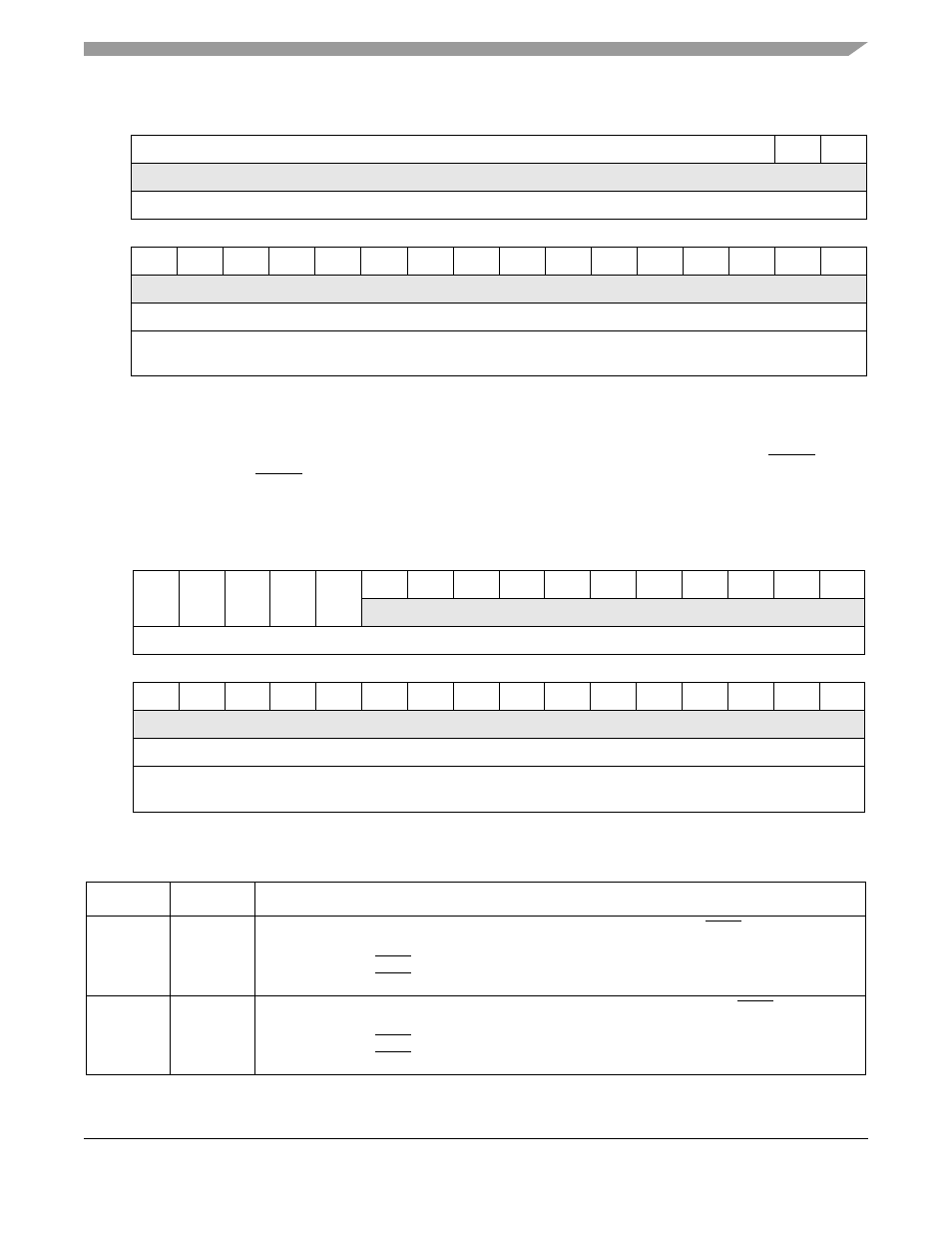

System Breakpoint Control Register (SBCR)

The System Breakpoint Control Register allows for discrete control over functionality of the BKPT signal.

The assertion of the BKPT signal can be programmed to halt the core, DMA, and DSPI or any

combination. In addition, a halt condition in the DMA can be programmed to halt the CPU, or a halt in the

CPU can halt the DMA.

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

R

BA

0

0

W

Reset

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

R

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

W

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Reg

Addr

CPU + 0xC0F

Figure 9-1. Module Base Address Register (MBAR)

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

R PIN2

CPU

PIN2

DMA

CPU2

DMA

DMA2

CPU

PIN2

DSPI

0

0

0

0

0

0

0

0

0

0

0

W

Reset

1

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

R

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

W

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Reg

Addr

MBAR + 0x0010

Figure 9-2. System Breakpoint Control Register (SBCR)

Table 9-2. SBCR Field Descriptions

Bit

Name

Description

31

PIN2CPU

Pin control of the ColdFire V4e breakpoint. This bit controls whether the BKPT pin can halt the

ColdFire V4e.

0 The assertion of BKPT will not halt the ColdFire V4e core.

1 The assertion of BKPT will halt the ColdFire V4e core.

30

PIN2DMA

Pin control of the multichannel DMA breakpoint. This bit controls whether the BKPT pin can halt

the DMA.

0 The assertion of BKPT will not halt the DMA.

1 The assertion of BKPT will halt the DMA.