5 rng interrupt mask register (rngimr), Rng interrupt mask register (rngimr) -49, P. 22-49 – Freescale Semiconductor MCF5480 User Manual

Page 651

RNG Execution Unit (RNG)

MCF548x Reference Manual, Rev. 3

Freescale Semiconductor

22-49

describes RNG interrupt status register fields.

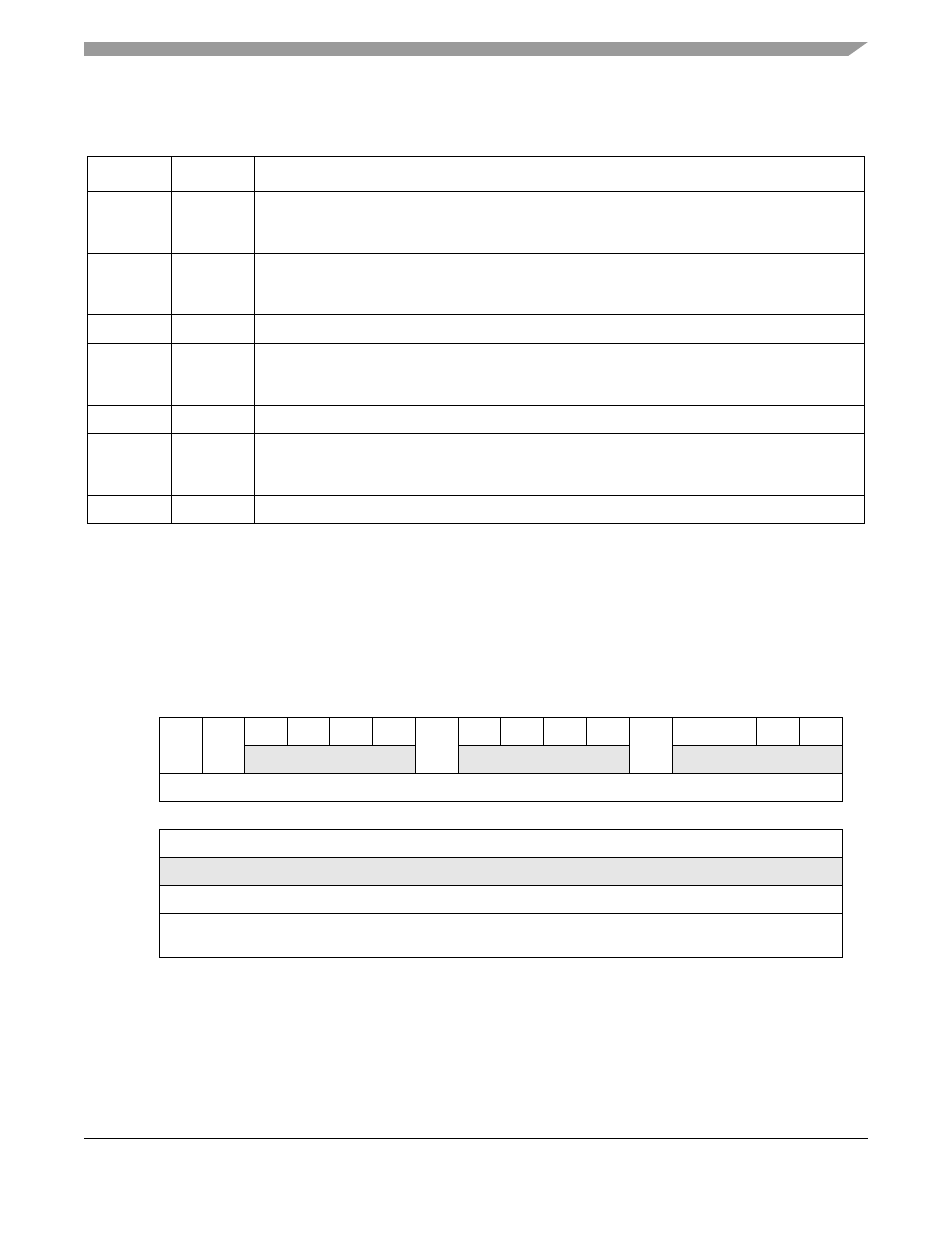

22.11.5 RNG Interrupt Mask Register (RNGIMR)

The RNG interrupt mask register controls the result of detected errors. For a given error, if the

corresponding bit in this register is set, then the error is disabled; no error interrupt occurs and the interrupt

status register is not updated to reflect the error. If the corresponding bit is not set, then upon detection of

an error, the interrupt status register is updated to reflect the error, causing assertion of the error interrupt

signal, and causing the module to halt processing.

describes RNG interrupt status register fields.

Table 22-32. RNGISR Field Descriptions

Bits

Name

Description

31

ME

Mode Error. Indicates that the host has attempted to write an illegal value to the mode register

0 Valid data

1 Invalid data error

30

AE

Address Error. An illegal read or write address was detected within the RNG address space.

0 No error detected

1 Address error

29–26

—

Reserved

25

OFU

Output FIFO Underflow. The RNG Output FIFO has been read while empty.

0 No underflow detected

1 Output FIFO has underflowed

24–21

—

Reserved

20

IE

Internal Error

0 No internal error detected

1 Internal error

19–0

—

Reserved

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

R

ME

AE

0

0

0

0

OFU

0

0

0

0

IE

0

0

0

0

W

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

R

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

W

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Reg

Addr

MBAR + 0x2E038