3 rng status register (rngsr), Rng status register (rngsr) -47, P. 22-47 – Freescale Semiconductor MCF5480 User Manual

Page 649: Table 22-30, Describes rng reset c

RNG Execution Unit (RNG)

MCF548x Reference Manual, Rev. 3

Freescale Semiconductor

22-47

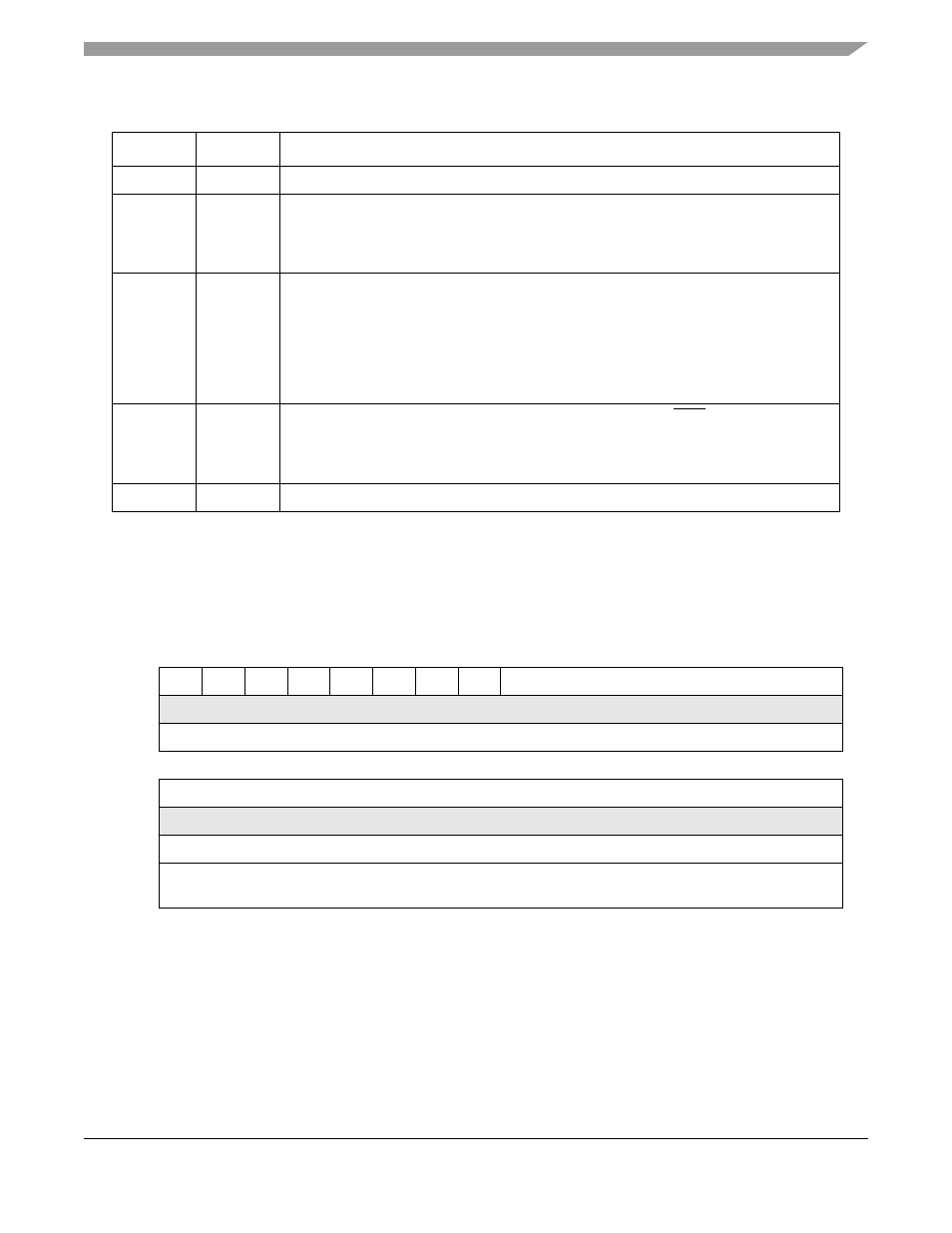

22.11.3 RNG Status Register (RNGSR)

This RNG status register,

, contains 4 bits which reflect the state of the RNG internal signals.

The RNG status register is read-only. Writing to this location will result in an address error being reflected

in the RNG interrupt status register.

describes RNG status register fields.

Table 22-30. RNGRCR Field Descriptions

Bits

Name

Description

31-27

—

Reserved

26

RI

Reset Interrupt. Writing this bit active high causes RNG interrupts signalling DONE and

ERROR to be reset. It further resets the state of the RNG interrupt status register.

0 No reset

1 Reset interrupt logic

25

MI

Module Initialization. This reset value performs enough of a reset to prepare the RNG for

another request, without forcing the internal control machines and the output FIFO to be

reset, thereby invalidating stored random numbers or requiring re-invocation of a warm-up

period. Module initialization is nearly the same as software reset, except that the interrupt

control register remains unchanged.

0 No reset

1 Reset most of RNG

24

SR

Software reset is functionally equivalent to hardware reset (the RSTI pin), but only for the

RNG. All registers and internal states are returned to their defined reset state.

0 No reset

1 Full RNG reset

23-0

—

Reserved

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

R

0

0

HALT

0

OFR

IE

0

RD

0

0

0

0

0

0

0

0

W

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

R

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

W

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Reg

Addr

MBAR + 0x2E028

Figure 22-34. RNG Status Register (RNGSR)