4 mii management frame register (mmfr), Mii management frame register (mmfr) -14 – Freescale Semiconductor MCF5480 User Manual

Page 944

MCF548x Reference Manual, Rev. 3

30-14

Freescale Semiconductor

30.3.3.4

MII Management Frame Register (MMFR)

The MMFR is accessed by the user and does not reset to a defined value. The MMFR register is used to

communicate with the attached MII compatible PHY devices, providing read/write access to their MII

registers. Performing a write to the MMFR will cause a management frame to be sourced unless the MSCR

has been programmed to 0. In the case of writing to MMFR when MSCR = 0, if the MSCR register is then

written to a non-zero value, an MII frame will be generated with the data previously written to the MMFR.

This allows MMFR and MSCR to be programmed in either order if MSCR is currently zero.

Table 30-9. ECR Field Descriptions

Bits

Name

Description

31–2

—

Reserved, should be cleared.

1

ETHER_EN When this bit is set, the FEC is enabled, and reception and transmission are possible. When this

bit is cleared, reception is immediately stopped and transmission is stopped after a bad CRC is

appended to any currently transmitted frame. The ETHER_EN bit is altered by hardware under the

following conditions:

• ECR[RESET] is set by software, in which case ETHER_EN will be cleared

• An error condition causes the EIR[XFERR], or EIR[RFERR] bits to set, in which case

ETHER_EN will be cleared

0

RESET

When this bit is set, the equivalent of a hardware reset is performed but it is local to the FEC.

ETHER_EN is cleared and all other FEC registers take their reset values. Also, any

transmission/reception currently in progress is abruptly aborted. This bit is automatically cleared by

hardware during the reset sequence. The reset sequence takes approximately 8 system clock

cycles after RESET is written with a 1.

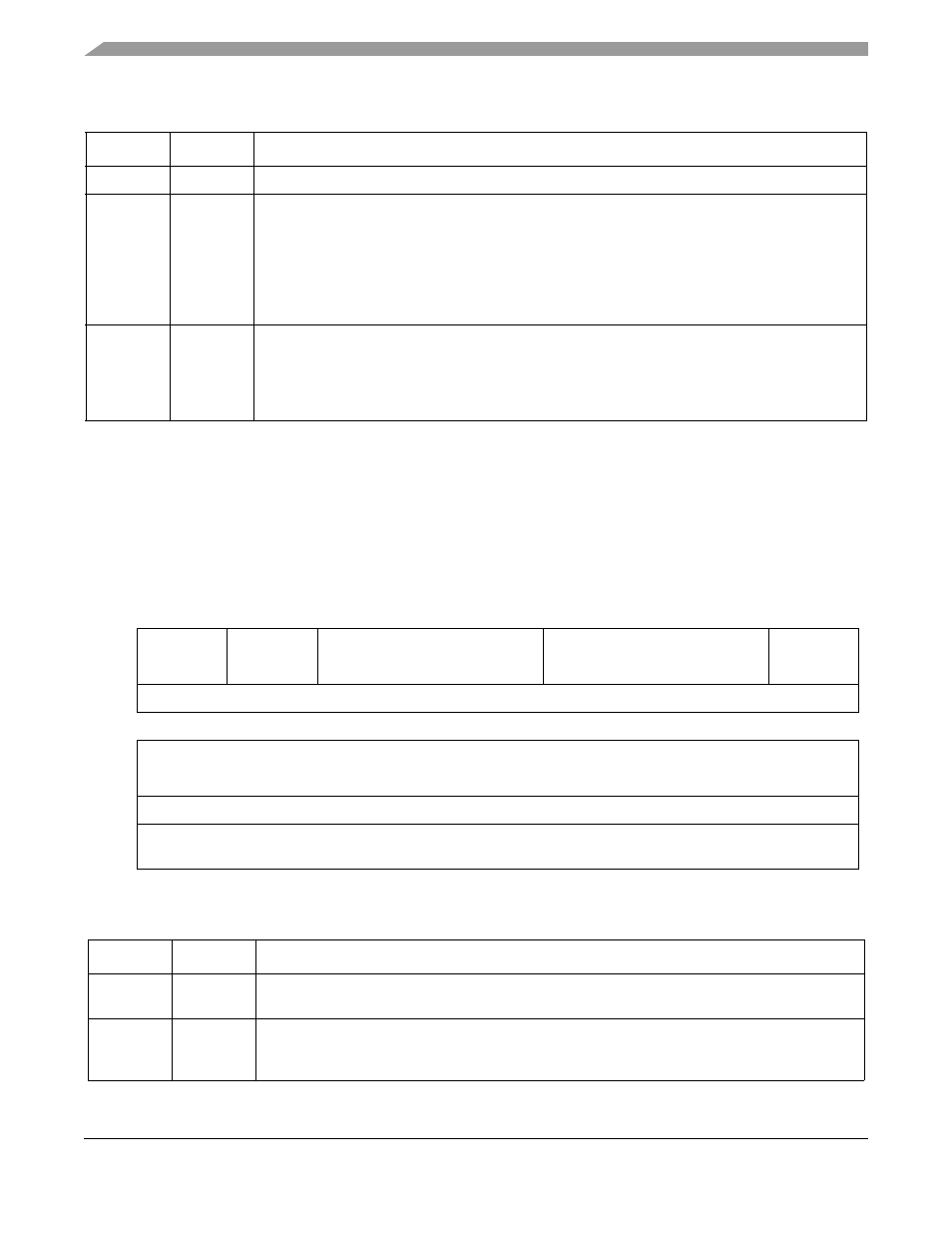

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

R

ST

OP

PA

RA

TA

W

Reset

Uninitialized

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

R

DATA

W

Reset

Uninitialized

Reg

Addr

MBAR + 0x9040 (FEC0), 0x9840 (FEC1)

Figure 30-5. MII Management Frame Register (MMFR)

Table 30-10. MMFR Field Descriptions

Bit

Name

Description

31–30

ST

Start of frame delimiter. These bits must be programmed to 0x01 for a valid MII management

frame.

29–28

OP

Operation code. This field must be programmed to 0x10 (read) or 0x01 (write) to generate a valid

MII management frame. A value of 0x11 will produce “read” frame operation while a value of 0x00

will produce “write” frame operation, but these frames will not be MII compliant.