6 sec id register (sidr), Sec id register (sidr) -16, P. 22-16 – Freescale Semiconductor MCF5480 User Manual

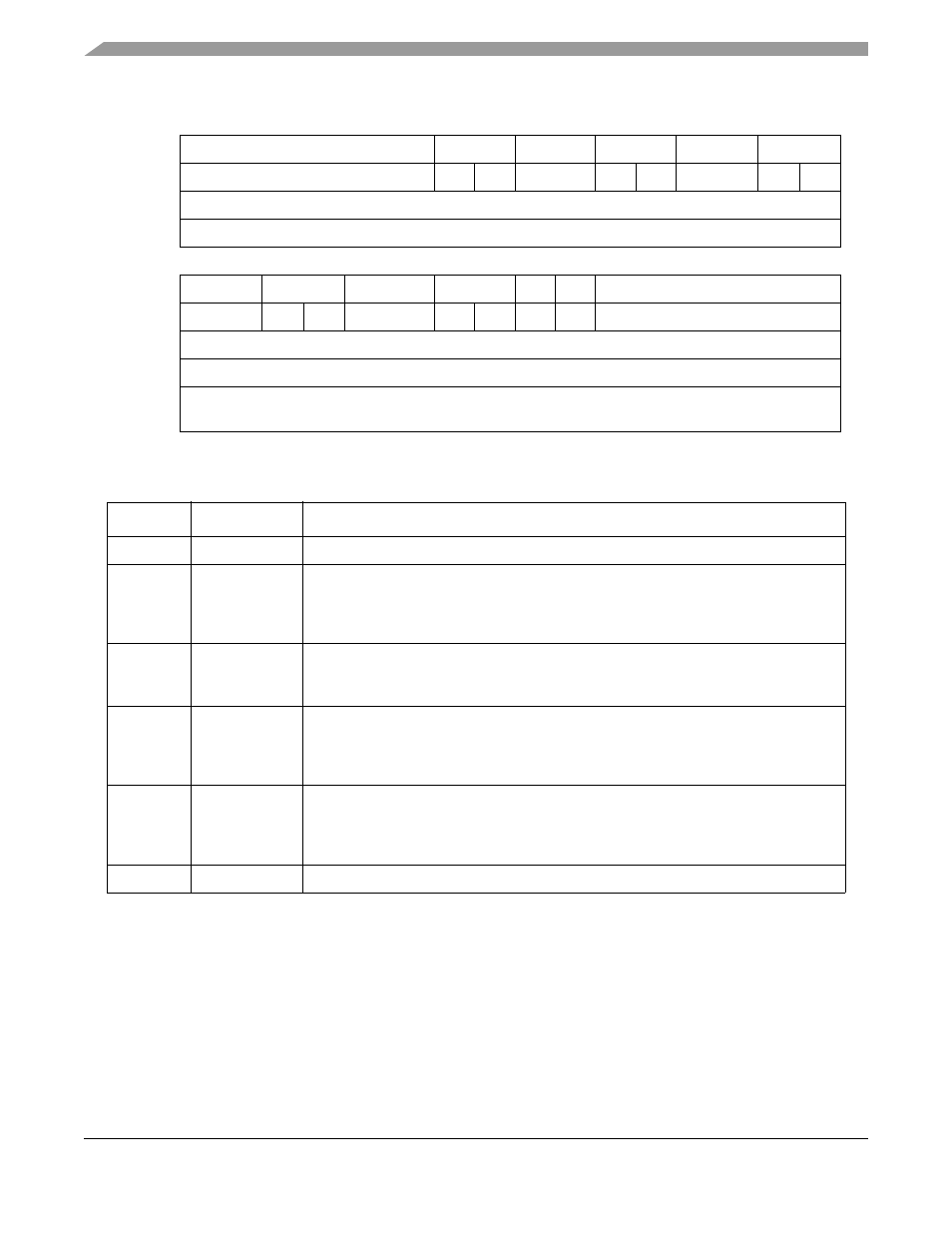

Page 618: Figure 22-12, Show the bit positions

MCF548x Reference Manual, Rev. 3

22-16

Freescale Semiconductor

22.6.4.6

SEC ID Register (SIDR)

The read-only SEC ID register, displayed in

, contains a 32-bit value that uniquely identifies

the version of the SEC. The value of this register is always 0x0900_0000.

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

Field

—

RNG

—

AFEU

—

MDEU

Definition

ERR

DN

ERR

DN

ERR

DN

Reset

0x0000

R/W

R/W

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Field

—

AESU

—

DEU

—

TEA

—

Definition

ERR

DN

ERR

DN

Reset

0x0000

R/W

R/W

Reg

Addr

MBAR + 0x2100C (SIMRL), 0x 21014 (SISRL), 0x2101C (SICRL)

Figure 22-12. SEC Interrupt Mask, Status, and Control Registers Low (SIMRL, SISRL, and SICRL)

Table 22-8. SIMRL, SISRL, and SICRL Field Descriptions

Bits

Name

Description

31–26

—

Reserved, should be cleared.

25, 21, 17,

13, 9

EU_x_ERR

EU error. Each of the execution units has an error bit.

0 No error detected.

1 Error detected. Indicates that execution unit status register must be read to determine

exact cause of the error.

24, 20, 16,

12, 8

EU_x_DN

EU done. Each of the execution units has a done bit.

0 Not DONE.

1 DONE bit indicates that the interrupting channel or EU has completed its operation.

23–22,

19–18,

15–14,

11–10, 7

—

Reserved, set to zero.

6

TEA

Transfer Error Acknowledge. Set when the SEC as a master receives a Transfer Error

Acknowledge.

0 No error detected.

1 TEA detected on Coldfire bus.

5–0

—

Reserved, set to zero.