6 emac instruction execution times, Emac instruction execution times -34, Table 3-18 shows timing for bcc instructions – Freescale Semiconductor MCF5480 User Manual

Page 138

MCF548x Reference Manual, Rev. 3

3-34

Freescale Semiconductor

shows timing for Bcc instructions.

3.7.6

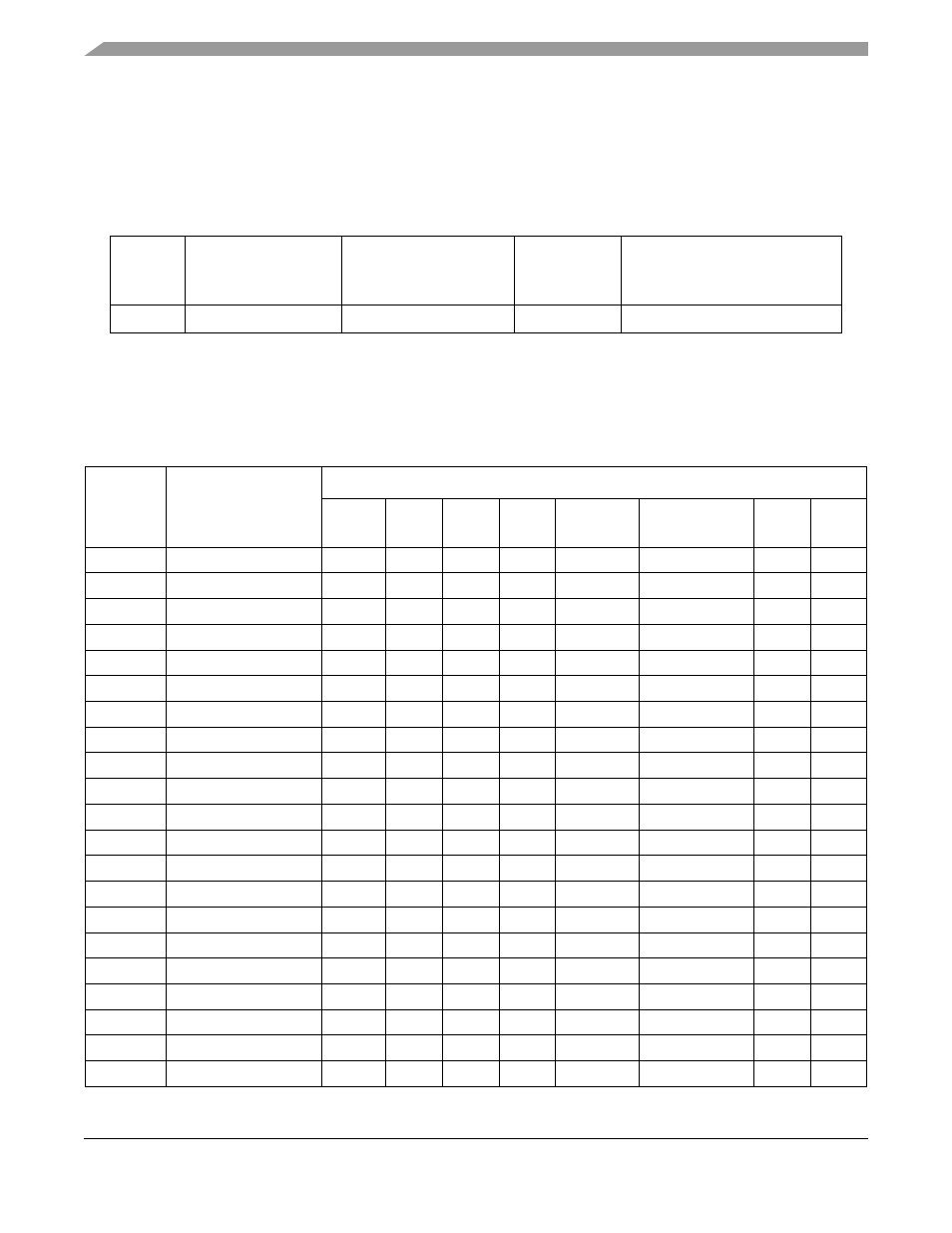

EMAC Instruction Execution Times

specifies instruction execution times associated with the enhanced multiply-accumulate

(EMAC) execute engine.

2

If predicted correctly by the hardware return stack.

3

If mispredicted by the hardware return stack.

4

If not predicted by the hardware return stack.

Table 3-18. Bcc Instruction Execution Times

Opcode

Branch Cache

Correctly Predicts

Taken

Prediction Table

Correctly Predicts Taken

Predicted

Correctly as

Not Taken

Predicted Incorrectly

bcc

0(0/0)

1(0/0)

1(0/0) 8(0/0)

Table 3-19. EMAC Instruction Execution Times

Opcode

Effective Address

Rn

(An)

(An)+

–(An)

(d16,An)

(d16,PC)

(d8,An,Xi*SF)

(d8,PC,Xi*SF)

xxx.wl

#xxx

mac.l

Ry,Rx,ACCx

1(0/0)

—

—

—

—

—

—

—

mac.l

Ry,Rx,

—

1(1/0)

1(1/0)

1(1/0)

1(1/0)

1

—

—

—

mac.w

Ry,Rx,ACCx

1(0/0)

—

—

—

—

—

—

—

mac.w

Ry,Rx,

—

1(1/0)

1(1/0)

1(1/0)

1(1/0)

1

—

—

—

mov.l

1(0/0)

—

—

—

—

—

—

1(0/0)

mov.l

ACCy,ACCx

1(0/0)

—

—

—

—

—

—

—

mov.l

8(0/0)

—

—

—

—

—

—

8(0/0)

mov.l

7(0/0)

—

—

—

—

—

—

7(0/0)

mov.l

1(0/0)

—

—

—

—

—

—

1(0/0)

mov.l

1(0/0)

—

—

—

—

—

—

1(0/0)

mov.l

ACCx,

1(0/0)

2

—

—

—

—

—

—

—

mov.l

MACSR,

1(0/0)

—

—

—

—

—

—

—

mov.l

MASK,

1(0/0)

—

—

—

—

—

—

—

mov.l

ACCext01,

1(0/0)

—

—

—

—

—

—

—

mov.l

ACCext23,

1(0/0)

—

—

—

—

—

—

—

msac.l

Ry,Rx,ACCx

1(0/0)

—

—

—

—

—

—

—

msac.l

Ry,Rx,

—

1(1/0)

1(1/0)

1(1/0)

1(1/0)

1

—

—

—

msac.w

Ry,Rx,ACCx

1(0/0)

—

—

—

—

—

—

—

msac.w

Ry,Rx,

—

1(1/0)

1(1/0)

1(1/0)

1(1/0)

1

—

—

—

muls.l

4(0/0)

4(1/0)

4(1/0)

4(1/0)

4(1/0)

—

—

—

muls.w

4(0/0)

4(1/0)

4(1/0)

4(1/0)

4(1/0)

5(1/0)

4(1/0)

4(0/0)