4 target control register (pcitcr), Target control register (pcitcr) -16 – Freescale Semiconductor MCF5480 User Manual

Page 500

MCF548x Reference Manual, Rev. 3

19-16

Freescale Semiconductor

19.3.2.3

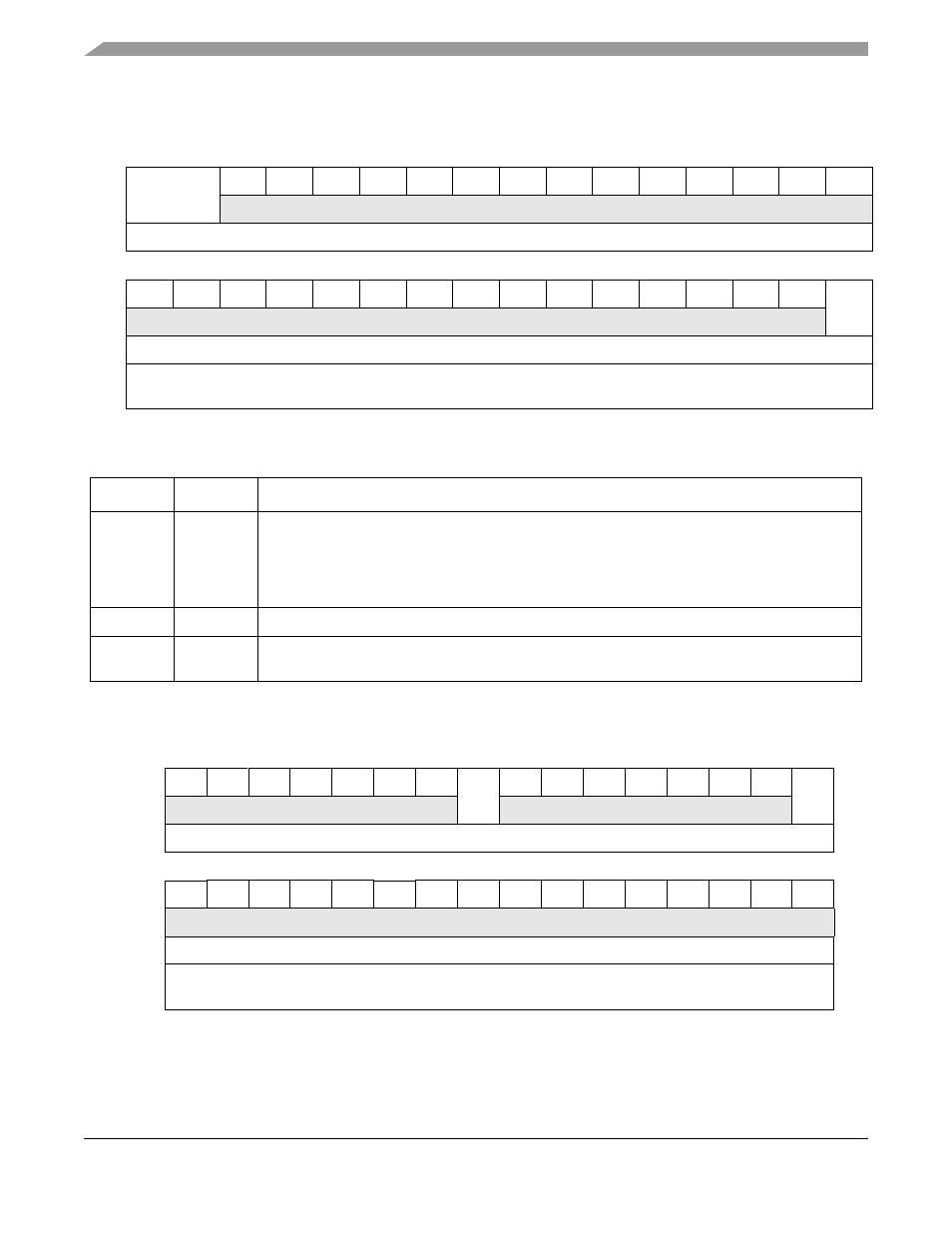

Target Base Address Translation Register 1 (PCITBATR1)

19.3.2.4

Target Control Register (PCITCR)

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

R Base Address

Translation 1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

W

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

R

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

EN

W

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Reg

Addr

MBAR + 0xB68

Figure 19-11. Target Base Address Translation Register 1 (PCITBATR1)

Table 19-12.

PCITBATR1 Field Descriptions

Bits

Name

Description

31–30

Base

Address

Translation

1

This base address register corresponds to a hit on the BAR1 in MCF548 PCI Type 0 Configuration

space register (PCI space). When there is a hit on MCF548 PCI BAR1 (MCF548 as Target), the

upper 2 bits of the address (1-Gbyte boundary) are written over by this register value to address

some 1-Gbyte space in MCF548. This register can be reprogrammed to move the window of

MCF548 address space accessed during a hit in PCIBAR1.

29–1

—

Reserved, should be cleared.

0

EN

This bit enables a transaction in BAR1 space. If this bit is zero and a hit on MCF548 PCI BAR1

occurs, the target interface gasket will abort the PCI transaction.

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

R

0

0

0

0

0

0

0

LD

0

0

0

0

0

0

0

P

W

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

R

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

W

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Reg

Addr

MBAR + 0xB6C

Figure 19-12. Target Control Register (PCITCR)