4 pci bus commands, Pci bus commands -51 – Freescale Semiconductor MCF5480 User Manual

Page 535

Functional Description

MCF548x Reference Manual, Rev. 3

Freescale Semiconductor

19-51

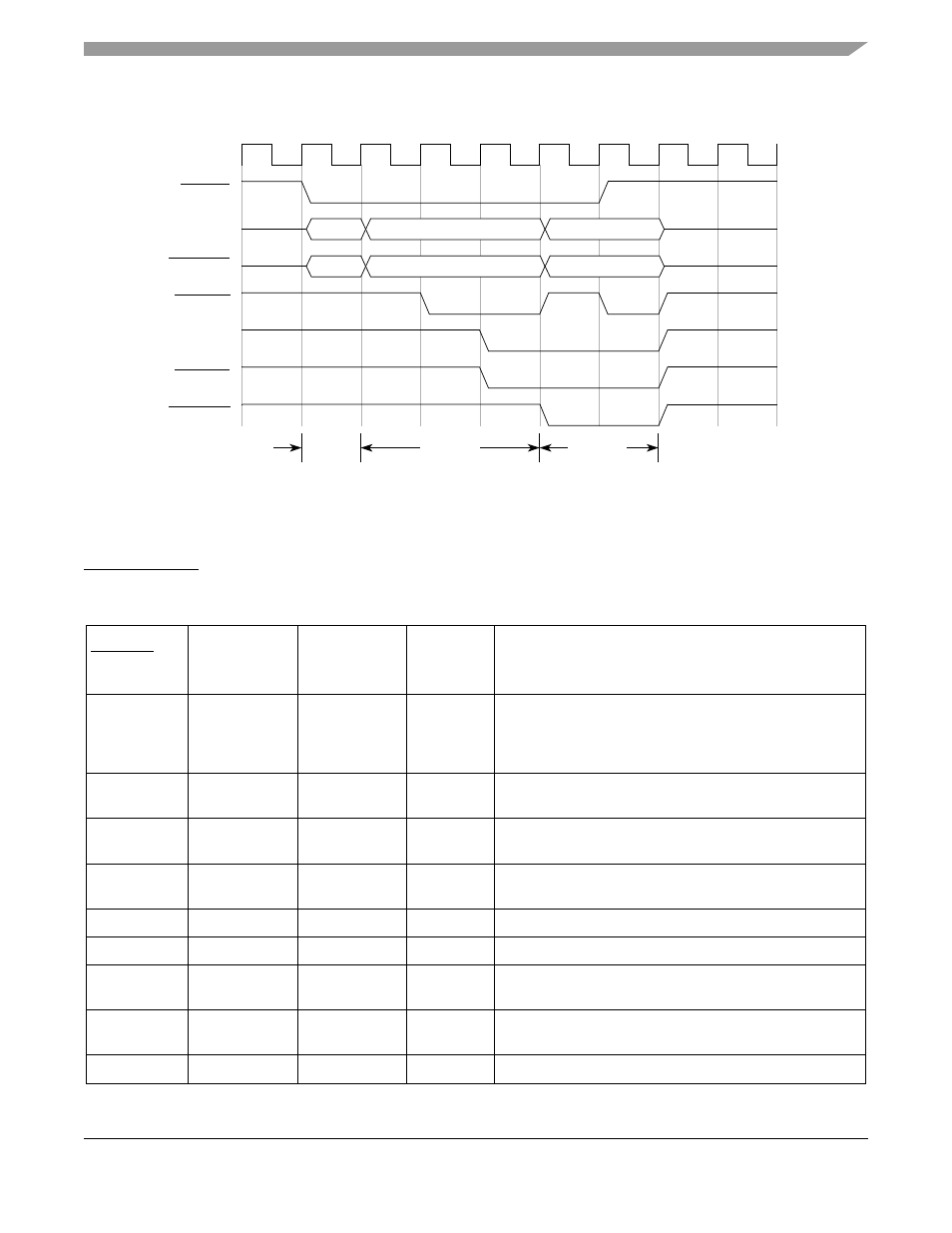

Figure 19-48. PCI Write Terminated by Target

19.4.1.4

PCI Bus Commands

PCI supports a number of different commands. These commands are presented by the initiator on the

PCICXBE[3:0] lines during the address phase of a PCI transaction.

Table 19-47. PCI Bus Commands

PCICXBE[3:0]

PCI Bus

Command

MCF548x

Supports as

Initiator

MCF548x

Supports

as Target

Definition

0000

Interrupt

Acknowledge

Yes

No

The interrupt acknowledge command is a read (implicitly

addressing an external interrupt controller). Only one

device on the PCI bus should respond to the interrupt

acknowledge command.

0001

Special Cycle

Yes

No

The Special Cycle command provides a mechanism to

broadcast select messages to all devices on the PCI bus.

0010

I/O read

Yes

No

The I/O read command accesses agents mapped into the

PCI I/O space.

0011

I/O write

Yes

No

The I/O write command accesses agents mapped into the

PCI I/O space.

0100

Reserved

No

No

—

0101

Reserved

No

No

—

0110

Memory-read

Yes

Yes

The memory read command accesses agents mapped into

PCI memory space.

0111

Memory-write

Yes

Yes

The memory write command accesses agents mapped into

PCI memory space.

1000

Reserved

No

No

—

Address

Phase

PCISTOP

Data

Phase 2

Data

Phase 1

PCI_CLK

FRAME

PCIAD

PCICXBE

PCIIRDY

PCITRDY

0

1

2

3

4

5

6

7

8

DEVSEL

A1

D1

D2

CMD

BYTE ENABLES

9

(Wait)

BYTE ENABLES