6 xl bus arbitration priority, Xl bus arbitration priority -75 – Freescale Semiconductor MCF5480 User Manual

Page 559

XL Bus Arbitration Priority

MCF548x Reference Manual, Rev. 3

Freescale Semiconductor

19-75

19.6

XL Bus Arbitration Priority

To prevent XL bus arbitration livelock, the PCI controller should have the same or higher XL bus

arbitration priority as other XL bus masters that access PCI space. If the XL bus arbiter master priority

register (PRI) is used, it should be programmed so that the PCI priority value has higher XL bus priority

than all other XL bus masters that address the PCI space through the XL bus slave interface of the PCI

Controller. XL bus masters that do not perform transactions to PCI across the XL internal bus can have

higher priority.

Note that the default priority setting uses the programmed priority settings where the G2 Core is set to

highest. If the Priority Register Enable is disabled for PCI (Master 3), the arbiter uses the hardware priority

values. The PCI hardwired priority is 0, highest. See

Section 20.3, “Register Definition,”

for more details.

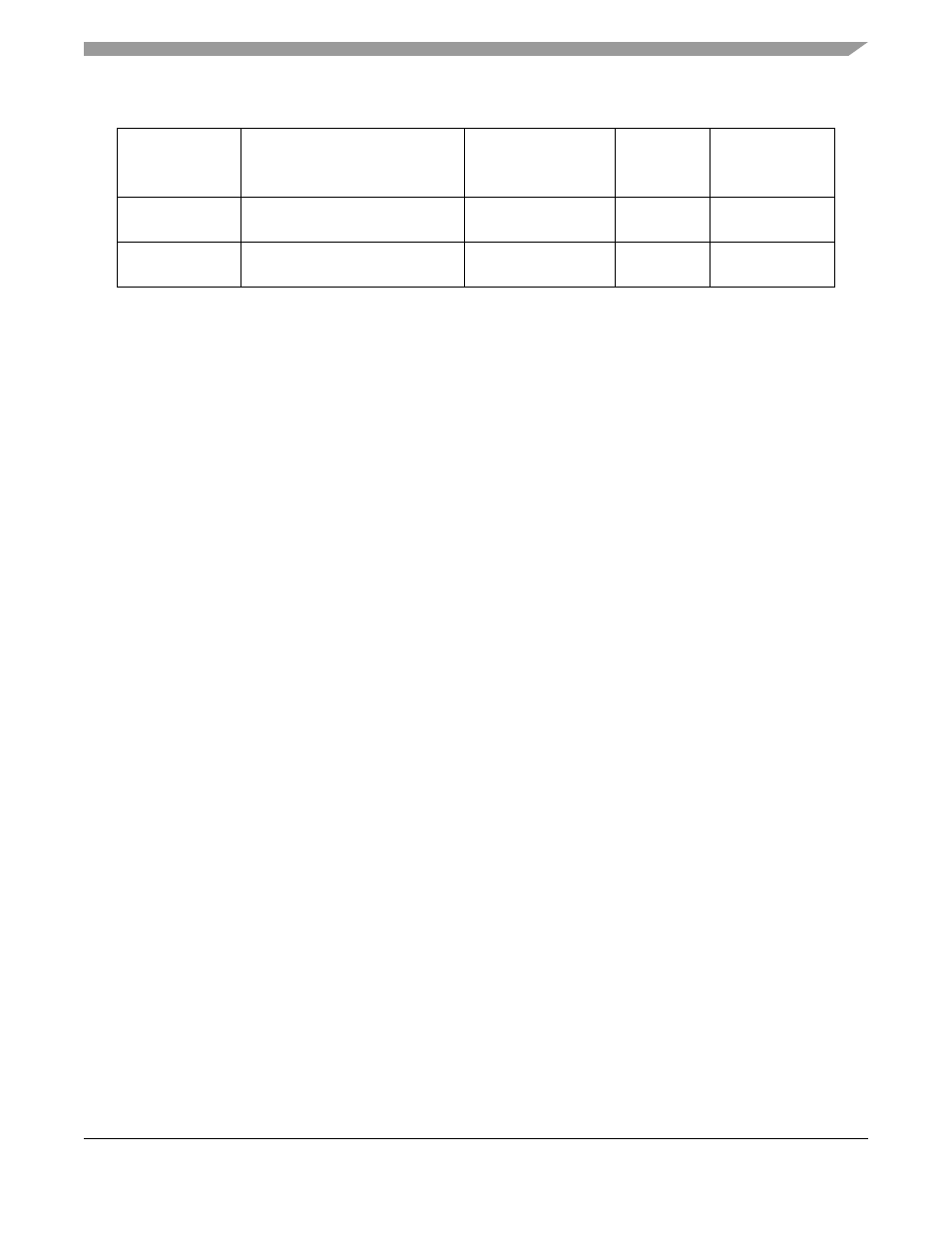

TBATR1

Target Base Address Translation

Register 0 (1 Gbyte)

X

X

IMWBAR

Initiator Window Base/Translation

Address Registers

X

X

Table 19-58. Address Register Accessibility (Continued)

Base Address

Register

Register Function

PCI Bus

Configuration

Access

Processor

Access

Any XL Bus

Master Access