11 rng execution unit (rng), 1 rng register map, 2 rng reset control register (rngrcr) – Freescale Semiconductor MCF5480 User Manual

Page 648: Rng execution unit (rng) -46, Rng register map -46, Rng reset control register (rngrcr) -46, P. 22-46

MCF548x Reference Manual, Rev. 3

22-46

Freescale Semiconductor

22.11 RNG Execution Unit (RNG)

The RNG is an execution unit capable of generating 32-bit random numbers. It is designed to comply with

the FIPS-140 standard for randomness and non-determinism. A linear feedback shift register (LSFR) and

cellular automata shift register (CASR) are operated in parallel to generate pseudo-random data.

22.11.1 RNG Register Map

The registers used in the RNG are documented primarily for debug and target mode operations. If the

requires the use of the RNG when acting as an initiator, accessing these registers directly is unnecessary.

The device drivers and the on-chip controller will abstract register level access from the user.

The single RNG contains the following registers:

•

Reset control register

•

Status register

•

Interrupt status register

•

Interrupt control register

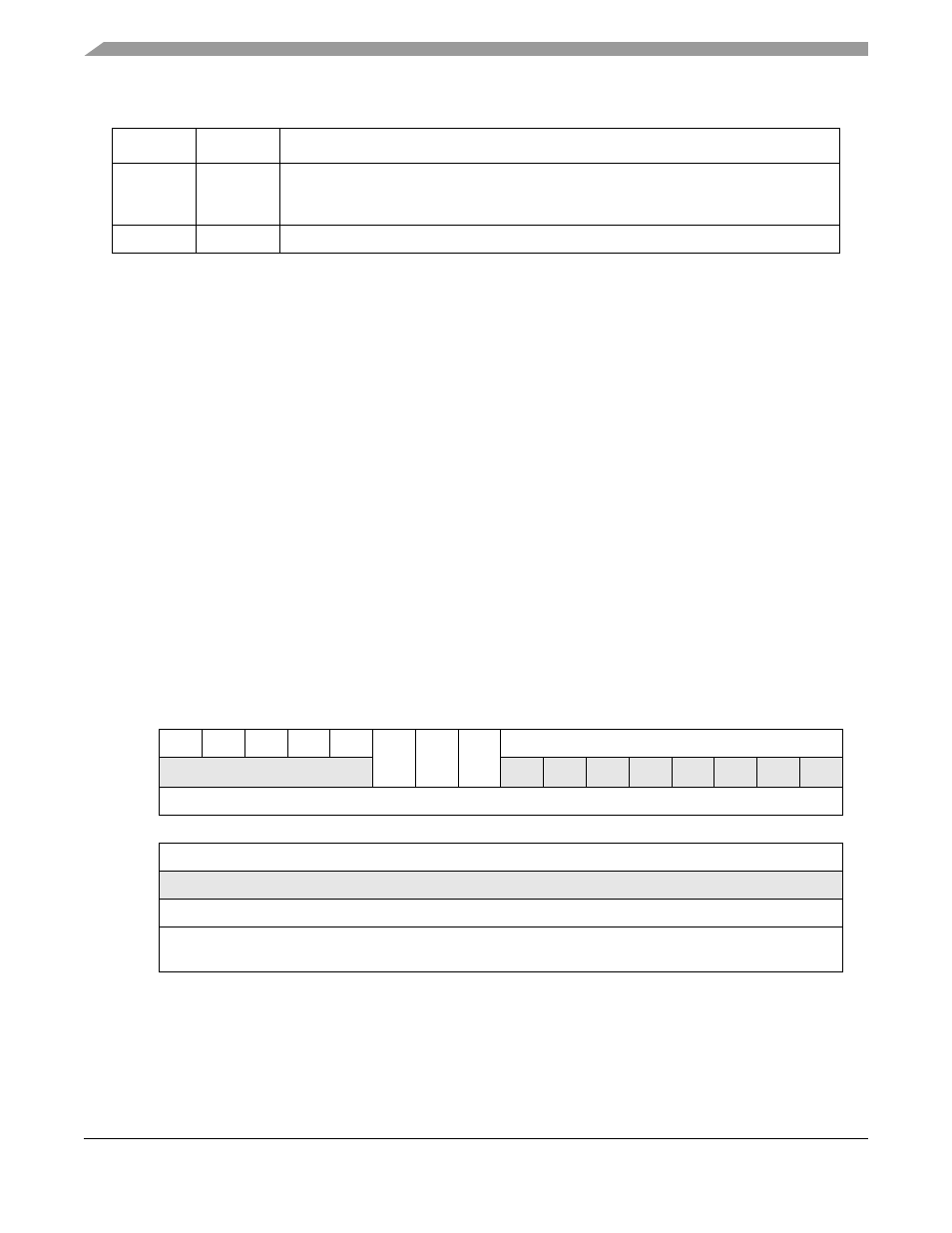

22.11.2 RNG Reset Control Register (RNGRCR)

This register, shown in

, contains three reset options specific to the RNG.

Figure 22-33. RNG Reset Control Register (RNGRCR)

describes RNG reset control register fields.

16

DSE

Data Size Error. An inconsistent value was written to the MDEU data size register:

0 Data size error enabled

1 Data size error disabled

15-0

—

Reserved, should be cleared.

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

R

0

0

0

0

0

RI

MI

SR

0

0

0

0

0

0

0

0

W

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

R

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

W

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Reg

Addr

MBAR + 0x2E018

Table 22-29. MDIMR Field Descriptions (Continued)

Bits

Name

Description