7 fpu instruction execution times, Fpu instruction execution times -35 – Freescale Semiconductor MCF5480 User Manual

Page 139

Instruction Execution Timing

MCF548x Reference Manual, Rev. 3

Freescale Semiconductor

3-35

Execution times for moving the contents of the ACC, ACCext[01,23], MACSR, or MASK into a

destination location

load, copy, MAC, or MSAC instructions are in the EMAC execution pipeline. In general, these store

operations require only a single cycle for execution, but if preceded immediately by a load, copy, MAC,

or MSAC instruction, the depth of the EMAC pipeline is exposed and the execution time is 4 cycles.

3.7.7

FPU Instruction Execution Times

specifies the instruction execution times associated with the FPU execute engine.

mulu.l

4(0/0)

4(1/0)

4(1/0)

4(1/0)

4(1/0)

—

—

—

mulu.w

4(0/0)

4(1/0)

4(1/0)

4(1/0)

4(1/0)

5(1/0)

4(1/0)

4(0/0)

1

Effective address of (d16,PC) not supported.

2

Storing the accumulator requires 1 additional clock cycle when saturation is enabled, or fractional rounding is performed

(MACSR[7:4] = 1---, -11-, --11).

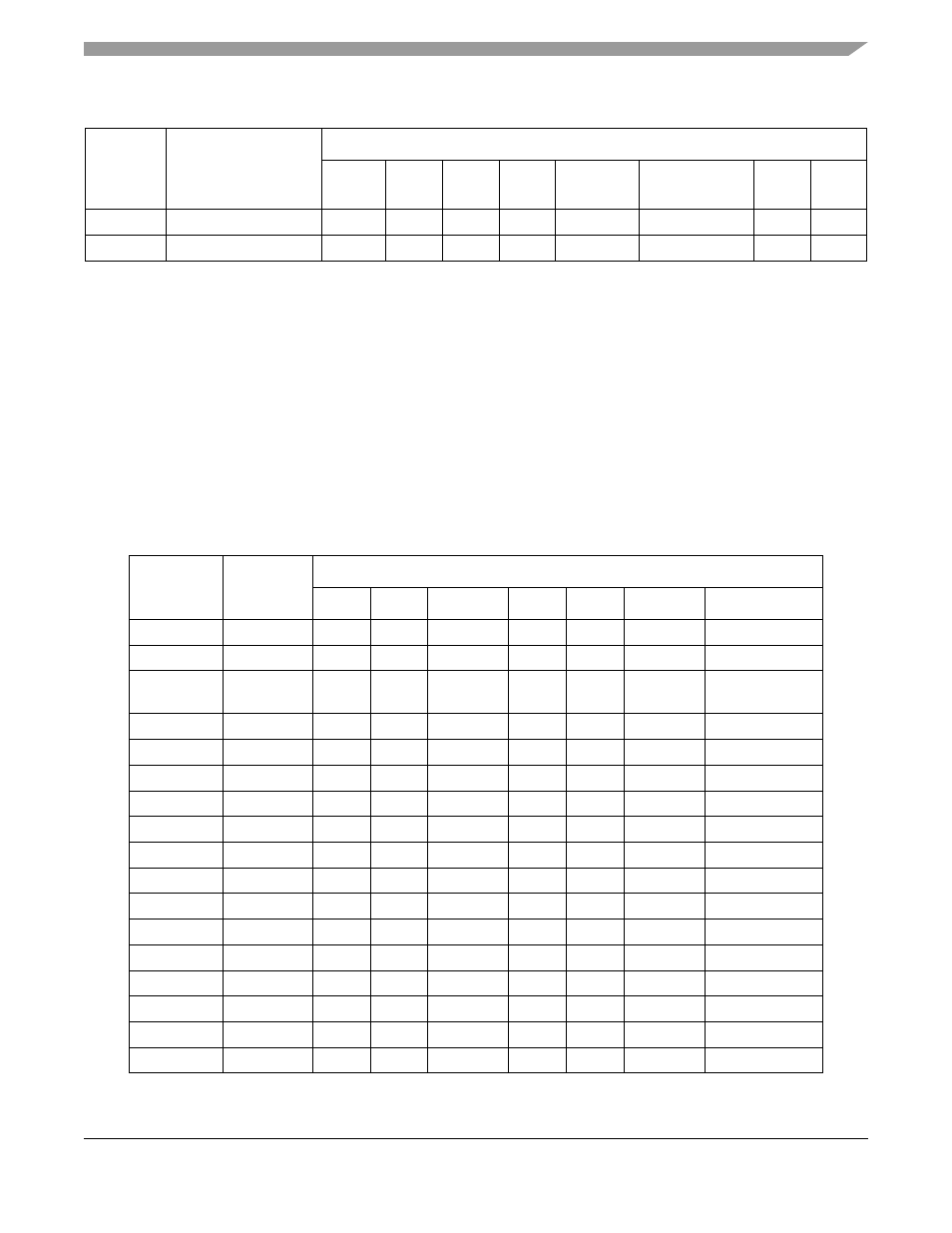

Table 3-20. FPU Instruction Execution Times

1,

2

Opcode

Format

Effective Address

FPn

Dn

(An)

(An)+

–(An)

(d

16

,An)

(d

16

,PC)

fabs

1(0/0)

1(0/0)

1(1/0)

1(1/0)

1(1/0)

1(1/0)

1(1/0)

fadd

4(0/0)

4(0/0)

4(1/0)

4(1/0)

4(1/0)

4(1/0)

4(1/0)

fbcc

—

—

—

—

—

—

2(0/0) if correct,

9(0/0) if incorrect

fcmp

4(0/0)

4(0/0)

4(1/0)

4(1/0)

4(1/0)

4(1/0)

4(1/0)

fdiv

23(0/0)

23(0/0)

23(1/0)

23(1/0)

23(1/0)

23(1/0)

23(1/0)

fint

4(0/0)

4(0/0)

4(1/0)

4(1/0)

4(1/0)

4(1/0)

4(1/0)

fintrz

4(0/0)

4(0/0)

4(1/0)

4(1/0)

4(1/0)

4(1/0)

4(1/0)

fmove

1(0/0)

1(0/0)

1(1/0)

1(1/0)

1(1/0)

1(1/0)

1(1/0)

fmove

FPy,

—

2(0/1)

2(0/1)

2(0/1)

2(0/1)

2(0/1)

—

fmove

—

6(0/0)

6(1/0)

6(1/0)

6(1/0)

6(1/0)

6(1/0)

fmove

FP*R,

—

1(0/0)

1(0/1)

1(0/1)

1(0/1)

1(0/1)

—

fmovem

3

—

—

2n(2n/0)

—

—

2n(2n/0)

2n(2n/0)

fmovem

3,

4

#list,

—

—

1+2n(0/2n)

—

—

1+2n(0/2n)

—

fmul

4(0/0)

4(0/0)

4(1/0)

4(1/0)

4(1/0)

4(1/0)

4(1/0)

fneg

1(0/0)

1(0/0)

1(1/0)

1(1/0)

1(1/0)

1(1/0)

1(1/0)

fnop

—

—

—

—

—

—

2(0/0)

frestore

—

—

6(4/0)

—

—

6(4/0)

6(4/0)

Table 3-19. EMAC Instruction Execution Times

Opcode

Effective Address

Rn

(An)

(An)+

–(An)

(d16,An)

(d16,PC)

(d8,An,Xi*SF)

(d8,PC,Xi*SF)

xxx.wl

#xxx