2 chip-select mask registers (csmr0-csmr5), Chip-select mask registers (csmr0–csmr5) -9, 2 chip-select mask registers (csmr0–csmr5) – Freescale Semiconductor MCF5480 User Manual

Page 425

Chip-Select Operation

MCF548x Reference Manual, Rev. 3

Freescale Semiconductor

17-9

17.5.2.2

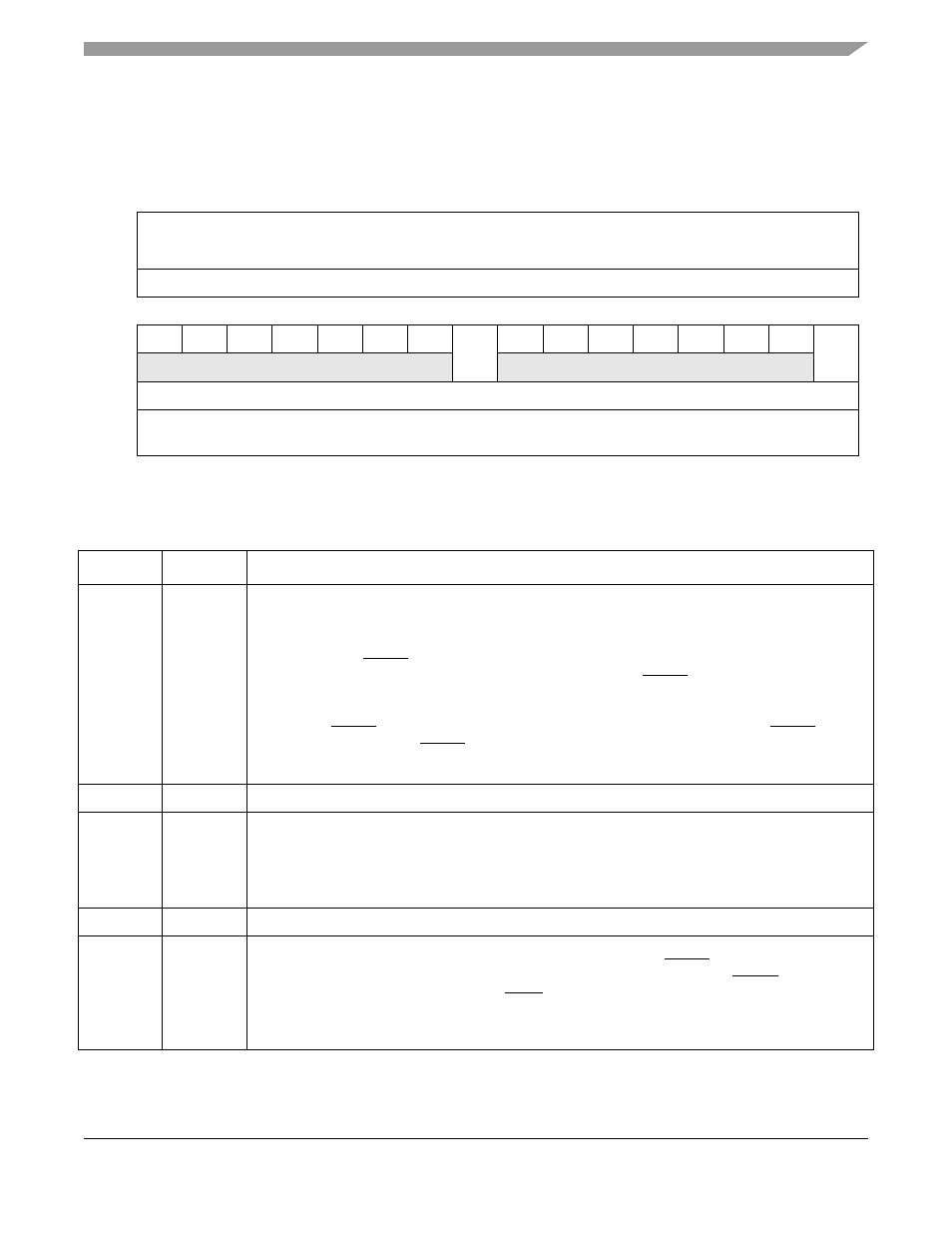

Chip-Select Mask Registers (CSMR0–CSMR5)

CSMRn,

, are used to specify the address mask and allowable access types for the respective

chip-selects.

describes CSMR fields.

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

R

BAM

W

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

R

0

0

0

0

0

0

0

WP

0

0

0

0

0

0

0

V

W

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Reg

Addr

MBAR + 0x504 (CSMR0); 0x510 (CSMR1); 0x51C (CSMR2);

0x528 (CSMR3); 0x534 (CSMR4); 0xr540 (CSMR5)

Figure 17-4. Chip-Select Mask Registers (CSMRn)

Table 17-8. CSMRn Field Descriptions

Bits

Name

Description

31–16

BAM

Base address mask. Defines the chip-select block size by masking address bits. Setting a BAM bit

causes the corresponding CSAR bit to be a “don’t care” in the decode.

0 Corresponding address bit is used in chip-select decode.

1 Corresponding address bit is a don’t care in chip-select decode.

The block size for FBCSn is 2

n

; n = (number of bits set in respective CSMR[BAM]) + 16.

For example, if CSAR0 = 0x0000 and CSMR0[BAM] = 0x0008, FBCS0 would address two

discontinuous 64-Kbyte memory blocks: one from 0x0000–0xFFFF and one from

0x8_0000–0x8_FFFF.

Likewise, for FBCS0 to access 32 Mbytes of address space starting at location 0x0, FBCS1 must

begin at the next byte after FBCS0 for a 16-Mbyte address space. Then CSAR0 = 0x0000,

CSMR0[BAM] = 0x01FF, CSAR1 = 0x0200, and CSMR1[BAM] = 0x00FF.

15–9

—

Reserved, should be cleared

8

WP

Write protect. Controls write accesses to the address range in the corresponding CSAR. Attempting

to write to the range of addresses for which CSARn[WP] = 1 results in the appropriate chip-select not

being selected. No exception occurs.

0 Both read and write accesses are allowed

1 Only read accesses are allowed

7–1

—

Reserved, should be cleared

0

V

Valid bit. Indicates whether the corresponding CSAR, CSMR, and CSCR contents are valid.

Programmed chip-selects do not assert until V bit is set (except for FBCS0, which acts as the global

chip-select). Reset clears each CSMRn[V]. At reset, no chip-select other than FBCS0 can be used

until the CSMR0[V] is set. At which point FBCS[5:0] functions as configured.

0 chip-select invalid

1 chip-select valid