8 usb endpoint n fifo alarm register (epnfar), Usb endpoint, 8 usb endpoint n fifo alarm register (ep n far) – Freescale Semiconductor MCF5480 User Manual

Page 918

MCF548x Reference Manual, Rev. 3

29-44

Freescale Semiconductor

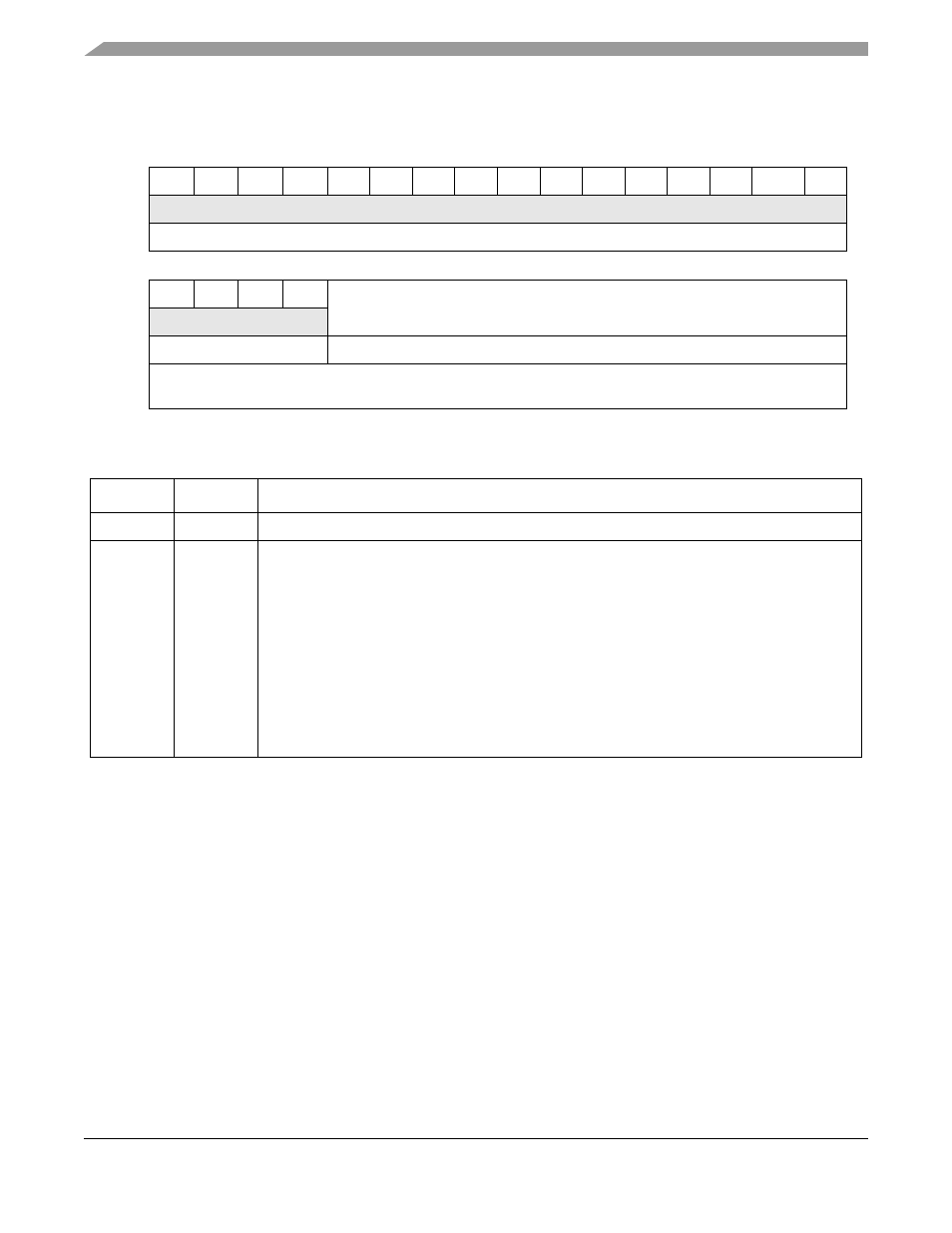

29.2.5.8

USB Endpoint n FIFO Alarm Register (EPnFAR)

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

R

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

W

Reset

Uninitialized

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

R

0

0

0

0

ALRMP

W

Reset

Uninitialized

0

0

0

0

0

0

0

0

0

0

0

0

Reg

Addr

MBAR + 0xB45C (EP0FAR); 0xB48C (EP1FAR); 0xB4BC (EP2FAR); 0xB4EC (EP3FAR);

0xB51C (EP4FAR); 0xB54C (EP5FAR); 0xB57C (EP6FAR)

Figure 29-48. USB Endpoint n Alarm Register (EPnFAR)

Table 29-43. EPnFAR Field Descriptions

Bits

Name

Description

31–12

—

Reserved, should be cleared.

11–0

ALRMP

Alarm pointer. The functionality of this field depends on the direction of the FIFO. The direction,

type, and packet size are defined in the EPnSTAT registers.

For Transmitter (IN): The user writes these bits to set the low level “watermark”, which is the point

at which the FIFO asserts its request for data filling to the DMA controller. This value is in bytes.

For example, with ALARM = 32, the alarm condition will occur when the FIFO has 32 (or less)

bytes in it. The alarm, once asserted, will not negate until the high level mark is reached, as

specified by the granularity bits in the EPnFCR.

For Receiver: The user writes these bits to set the low level “watermark”, which is the point at

which the FIFO asserts its request for data emptying to the DMA controller. This value is in bytes.

For example, with ALARM = 32, the alarm condition will occur when the FIFO has 32 (or less) free

bytes in it. The alarm, once asserted will not negate until the high level mark is reached, as

specified by the granularity bits in the EPnFCR.