3 interrupt force registers (intfrch, intfrcl), Interrupt force registers (intfrch, intfrcl) -8 – Freescale Semiconductor MCF5480 User Manual

Page 360

MCF548x Reference Manual, Rev. 3

13-8

Freescale Semiconductor

13.2.1.3

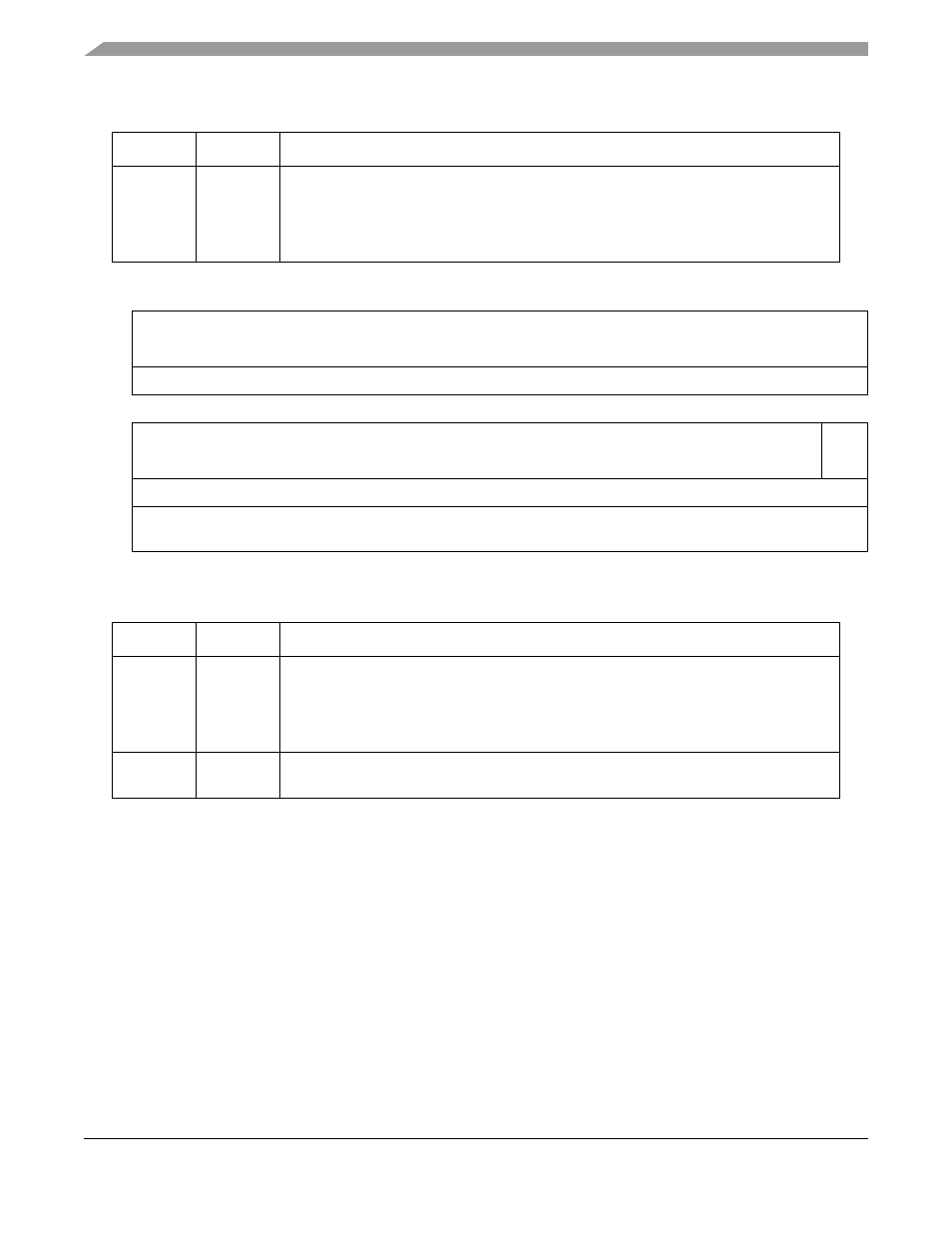

Interrupt Force Registers (INTFRCH, INTFRCL)

The INTFRCH and INTFRCL registers are each 32 bits in size and provide a mechanism to allow software

generation of interrupts for each possible source for functional or debug purposes. The system design may

reserve one or more sources to allow software to self-schedule interrupts by forcing one or more of these

bits in the appropriate INTFRC register (1 = force request, 0 = negate request). The assertion of an interrupt

request via the INTFRC register is not affected by the interrupt mask register. The INTFRC register is

cleared by reset.

Table 13-5. IMRH Field Descriptions

Bits

Name

Description

31–0

INT_MASK Interrupt mask. Each bit corresponds to an interrupt source. The corresponding IMRH bit

determines whether an interrupt condition can generate an interrupt. The corresponding

IPRH bit reflects the state of the interrupt signal even if the corresponding IMRH bit is set.

0 The corresponding interrupt source is not masked

1 The corresponding interrupt source is masked

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

R

INT_MASK[31:16]

W

Reset

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

R

INT_MASK[15:1]

MASK

ALL

W

Reset

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

Reg

Addr

MBAR + 0x70C

Figure 13-4. Interrupt Mask Register Low (IMRL)

Table 13-6. IMRL Field Descriptions

Bits

Name

Description

31–1

INT_MASK Interrupt mask. Each bit corresponds to an interrupt source. The corresponding IMRL bit

determines whether an interrupt condition can generate an interrupt. The corresponding

IPRL bit reflects the state of the interrupt signal even if the corresponding IMRL bit is set.

0 The corresponding interrupt source is not masked

1 The corresponding interrupt source is masked

0

MASKALL

Mask all interrupts. Setting this bit will force the other 63 bits of the IMRH and IMRL to ones,

disabling all interrupt sources, and providing a global mask-all capability.