9 expansion rom base address pcierbar-pci dword c, 11 configuration 2 register (pcicr2)-pci dword f, 2 general control/status registers – Freescale Semiconductor MCF5480 User Manual

Page 497: Configuration 2 register (pcicr2)—pci dword f -13, General control/status registers -13, 9 expansion rom base address pcierbar—pci dword c, 11 configuration 2 register (pcicr2)—pci dword f

Memory Map/Register Definition

MCF548x Reference Manual, Rev. 3

Freescale Semiconductor

19-13

All 32 bits of the register are programmable by the slave bus. From the PCI bus, this register can only be

read, not written. The reset value is 0x0000_0000 and is accessible at address MBAR + 0xB2C.

19.3.1.9

Expansion ROM Base Address PCIERBAR—PCI Dword C

Not implemented. Fixed to 0x0000_0000 at address MBAR + 0xB30.

19.3.1.10 Capabilities Pointer (Cap_Ptr) PCICPR—PCI Dword D

Not implemented. Fixed to 0x00 at address MBAR + 0xB34.

19.3.1.11 Configuration 2 Register (PCICR2)—PCI Dword F

19.3.2

General Control/Status Registers

The general control/status registers primarily address the configurability of the XL bus initiator and target

interfaces, though some also address global options which affect the multichannel DMA interface. These

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

R

Max_Lat

Min_Gnt

W

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

R

Interrupt Pin

Interrupt Line

W

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Reg

Addr

MBAR + 0xB3C

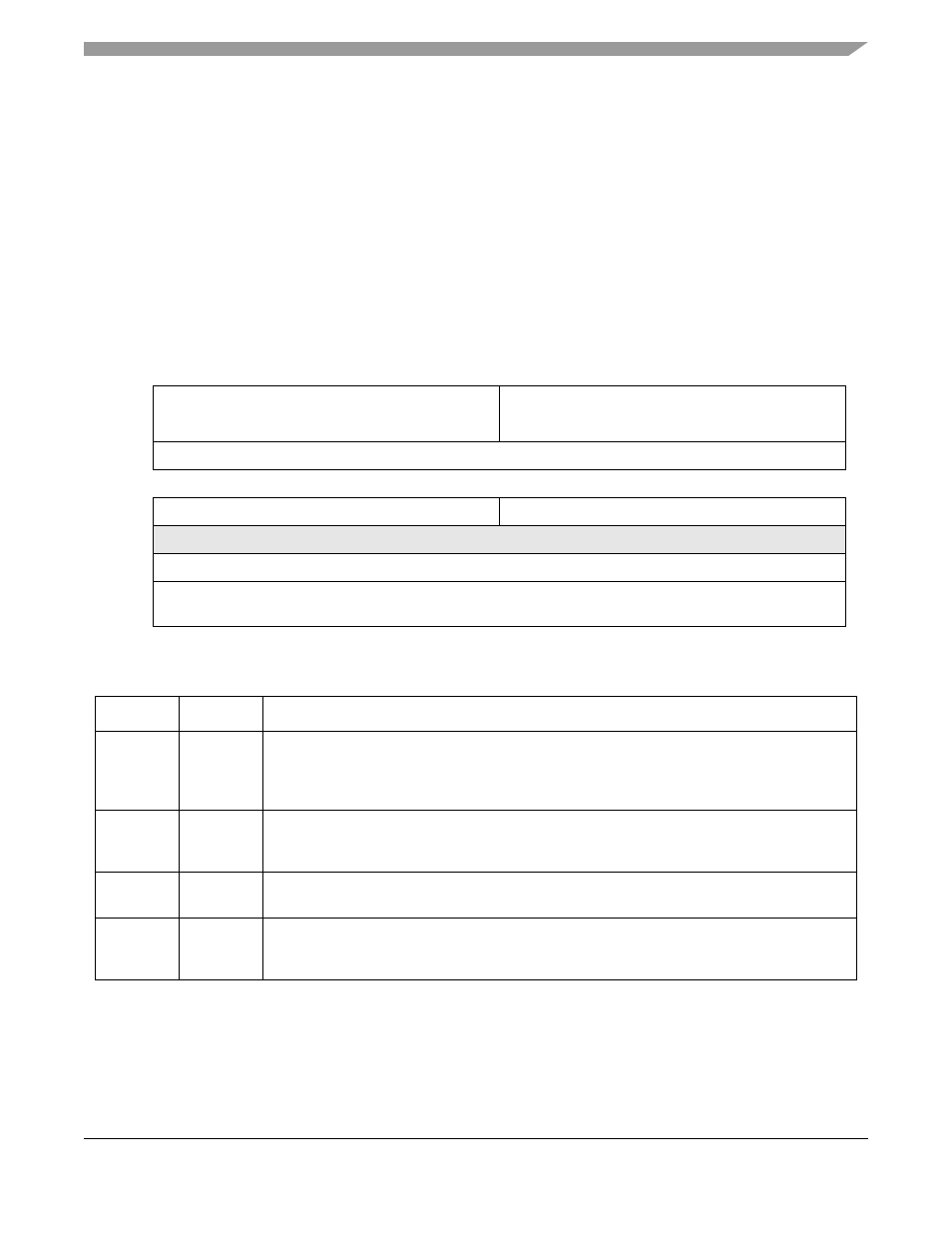

Figure 19-8. Configuration 2 Register (PCICR2)

Table 19-9. PCICR2 Field Descriptions

Bits

Name

Description

31–24

Max_Lat

Maximum latency. Specifies how often, in units of 1/4 microseconds, the PCI controller would

like to have access to the PCI bus as master. A value of zero indicates the device has no

stringent requirement in this area. The register is read/write to/from the slave bus, but read only

from the PCI bus.

23–16

Min_Gnt

Minimum grant. The value programmed to this register indicates how long the PCI controller as

master would like to retain PCI bus ownership whenever it initiates a transaction. The register is

programmable from the slave bus, but read only from the PCI bus.

15–8

Interrupt

Pin

Fixed to 0x00. Indicates that this device does not use an interrupt request pin.

7–0

Interrupt

Line

Fixed to 0x00. The Interrupt Line register stores a value that identifies which input on a PCI

interrupt controller the function’s PCI interrupt request pin. Since no interrupt request pin is used,

as specified in the Interrupt Pin register, this register has no function.