12 cache operation summary, 1 instruction cache state transitions, Cache operation summary -26 – Freescale Semiconductor MCF5480 User Manual

Page 246: Instruction cache state transitions -26

MCF548x Reference Manual, Rev. 3

7-26

Freescale Semiconductor

7.12

Cache Operation Summary

This section gives operational details for the cache and presents instruction and data cache-line state

diagrams.

7.12.1

Instruction Cache State Transitions

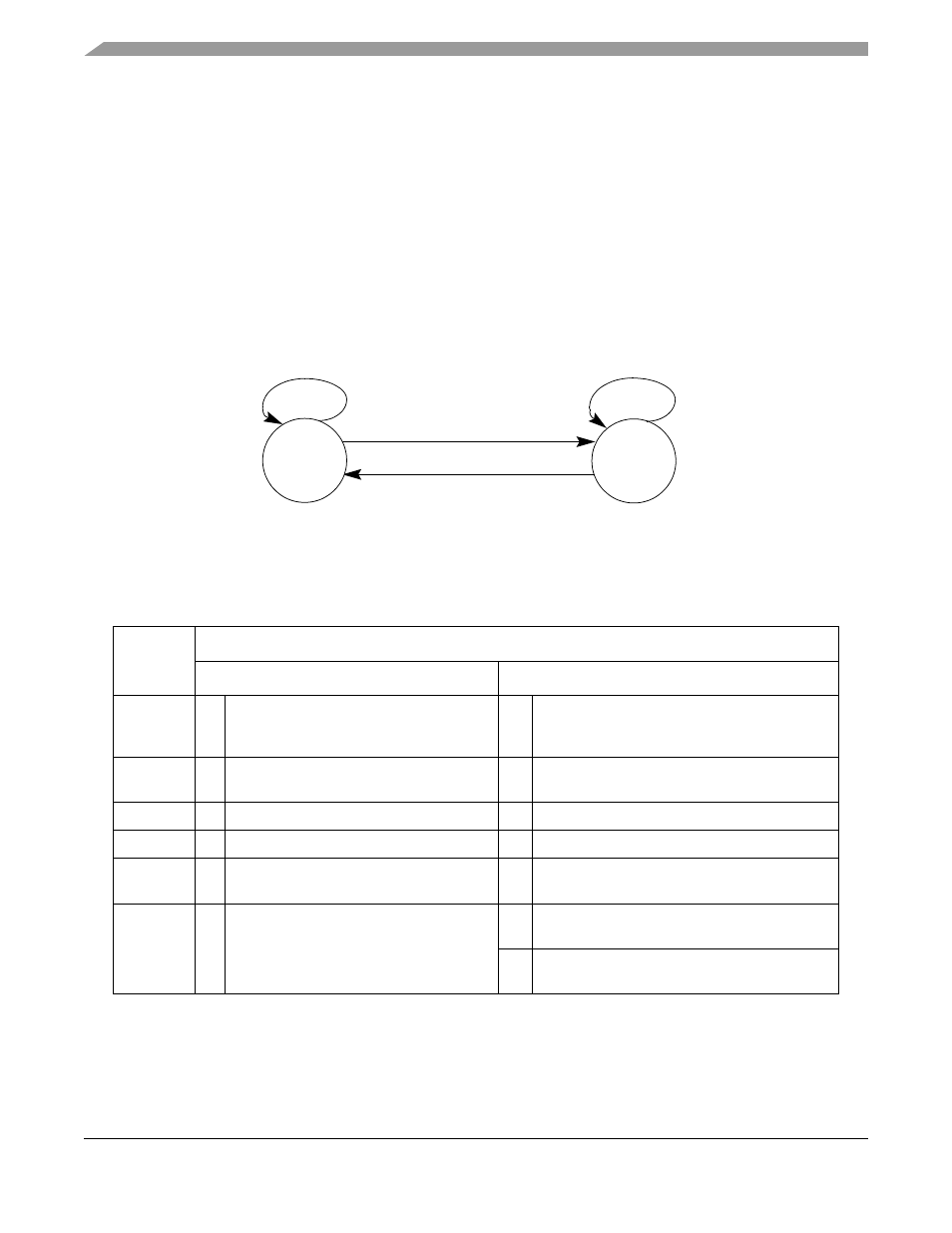

Because the instruction cache does not support writes, it supports fewer operations than the data cache. As

shows, an instruction cache line can be in one of two states, valid or invalid. Modified state is

not supported. Transitions are labeled with a capital letter indicating the previous state and a number

indicating the specific case listed in

. These numbers correspond to the equivalent operations on

data caches, described in

Section 7.12.2, “Data Cache State Transitions

.”

Figure 7-12. Instruction Cache Line State Diagram

describes the instruction cache state transitions shown in

.

Table 7-6. Instruction Cache Line State Transitions

Access

Current State

Invalid (V = 0)

Valid (V = 1)

Read miss

II1

Read line from memory and update cache;

supply data to processor;

go to valid state.

IV1

Read new line from memory and update cache;

supply data to processor; stay in valid state.

Read hit

II2

Not possible

IV2

Supply data to processor;

stay in valid state.

Write miss

II3

Not possible

IV3

Not possible

Write hit

II4

Not possible

IV4

Not possible

Cache

invalidate

II5

No action;

stay in invalid state.

IV5

No action;

go to invalid state.

Cache

push

II6,

II7

No action;

stay in invalid state.

IV6

No action;

go to invalid state.

IV7

No action;

stay in valid state.

Valid

V = 1

II5—ICINVA

II6—CPUSHL & IDPI

II7—CPUSHL & IDPI

IV1—CPU read miss

IV2—CPU read hit

IV7—CPUSHL & IDPI

IV5—ICINVA

IV6—CPUSHL & IDPI

Invalid

V = 0

II1—CPU read miss