27 fec transmit fifo status register (fectfsr), Fec transmit fifo status register (fectfsr) -34 – Freescale Semiconductor MCF5480 User Manual

Page 964

MCF548x Reference Manual, Rev. 3

30-34

Freescale Semiconductor

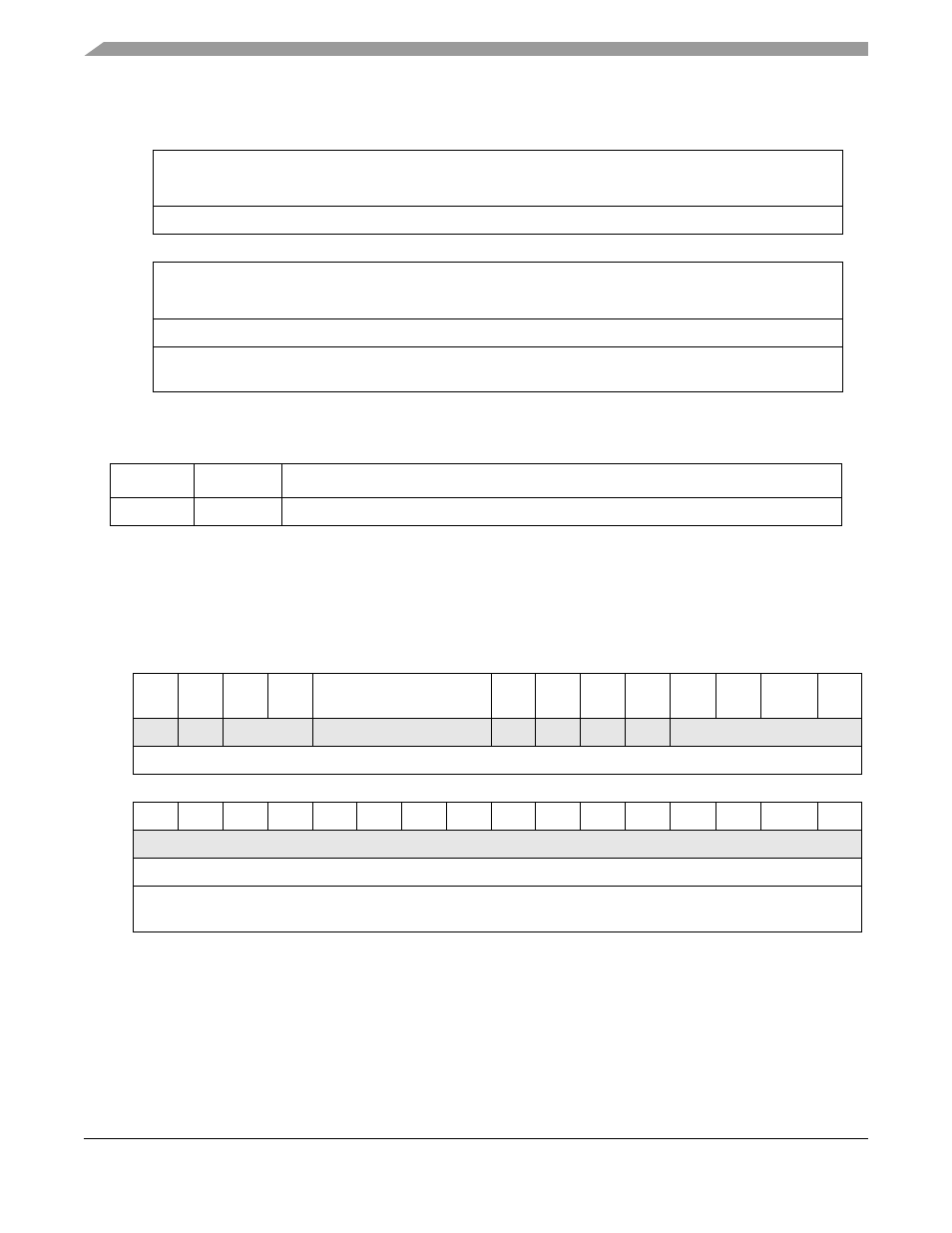

30.3.3.27 FEC Transmit FIFO Status Register (FECTFSR)

The FIFO transmit status register contains bits which provide information about the status of the FIFO

controller. Some of the bits of this register are used to generate DMA requests.

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

R

FIFO_DATA

W

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

R

FIFO_DATA

W

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Reg

Addr

MBAR + 0x91A4 (FEC0), 0x99A4 (FEC1)

Figure 30-29. FEC Transmit FIFO Data Register (FECTFDR)

Table 30-33. FECTFDR Field Descriptions

Bits

Name

Descriptions

31–0

FIFO_DATA Transmit FIFO data. Writing to this register will fill the Tx FIFO with transmit data.

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

R

IP

TXW

0

0

FRM

FAE

0

UF

OF

FRM

RDY

FU

ALARM EMT

W

w1c

w1c

w1c

w1c

w1c

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

1

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

R

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

W

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Reg

Addr

MBAR + 0x91A8 (FEC0), 0x99A8 (FEC1)

Figure 30-30. FEC Transmit FIFO Status Register (FECTFSR)