6 ptd control (ptd), Ptd control (ptd) -9 – Freescale Semiconductor MCF5480 User Manual

Page 729

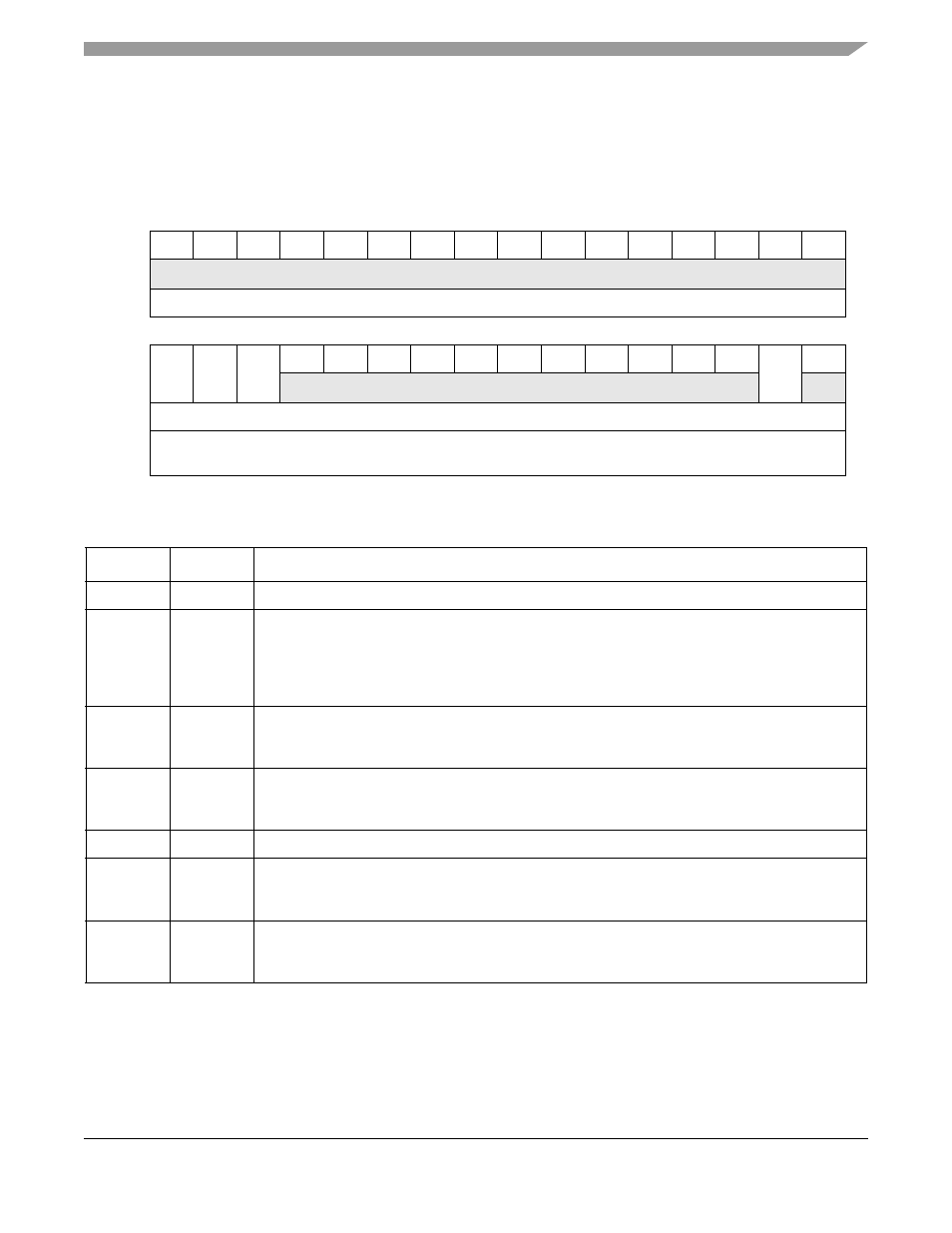

Memory Map/Register Definitions

MCF548x Reference Manual, Rev. 3

Freescale Semiconductor

24-9

24.3.3.6

PTD Control (PTD)

The priority task decode control register is used to configure different operating modes of this DMA

module. The PTD is also used to enable/disable new functionality designed into the module after the first

release of the design.

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

R

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

W

Reset

0

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

15

14

13

12

11

10

9

8

7

5

5

4

3

2

1

0

R PCTL

15

PCTL

14

PCTL

13

0

0

0

0

0

0

0

0

0

0

0

PCTL

1

0

W

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Reg

Addr

MBAR + 0x8010

Figure 24-7. PTD Control Register (PTD)

Table 24-6. PTD Field Descriptions

Bits

Name Description

31–16

—

Reserved.

15

PCTL15

Task priority control. This bit selects the prioritization scheme used by the DMA when deciding

which tasks to run. This is a global bit and affects all DMA channels. See

and

Section 24.3.3.10, “Priority Registers (PRIORn),”

for further reference.

1 Task priority

0 Request priority

14

PCTL14

Bus error control

0 Enable interrupt for bus error

1 Disable interrupt for bus error

13

PCTL13

Task arbitration control

0 Do not force arbitration

1 Force arbitration for higher task number on same request level

12–2

—

Reserved

1

PCTL1

Registered request control

0 Take request straight from FIFO controller

1 Enable registered Requester from prefetch buffer

0

PCTL0

CommBus Prefetch

1 disable prefetch

0 enable prefetch