4 usb descriptor ram data register (dramdr), Usb descriptor ram data register (dramdr) -13 – Freescale Semiconductor MCF5480 User Manual

Page 887

Memory Map/Register Definition

MCF548x Reference Manual, Rev. 3

Freescale Semiconductor

29-13

29.2.2.4

USB Descriptor RAM Data Register (DRAMDR)

The DRAMDR allows user access to the USB descriptor memory.

Table 29-4. DRAMCR Field Descriptions

Bits

Name

Description

31

START

Start. This bit initiates the GET_DESCRIPTOR handler. Before setting this bit, the software must

set the DSIZE[10:0] and DADR[9:0] values to the appropriate values for the current

GET_DESCRIPTOR request. This bit automatically resets to 0 after a write. Writing a 0 to this bit

has no effect.

30

BSY

Busy. This read only bit is the GET_DESCRIPTOR handler busy signal.

0 The GET_DESCRIPTOR handler is idle.

1 The GET_DESCRIPTOR handler is busy sending the specified descriptor to the USB.

29–27

—

Reserved, should be cleared.

26–16

DSIZE

Descriptor size. This is the descriptor size. When the GET_DESCRIPTOR handler is initiated, this

value should be set to the length of the requested descriptor within the descriptor RAM.

15–10

—

Reserved, should be cleared.

9–0

DADR

Descriptor address. This is the descriptor offset in bytes from the RAM base address. This register

allows user access to the USB descriptor RAM and is also used by the GET_DESCRIPTOR handler

when servicing GET_DESCRIPTOR requests.

For user access: The user programs a desired address into the DADR[9:0] bits, then follows it with

a read or write to the DRAMDR register to complete the access. Upon read/write access to

DRAMDR, the address in DADR will increment automatically.

For GET_DESCRIPTOR handler access: When the GET_DESCRIPTOR handler is initiated, this

value should be set to the address within the descriptor RAM of the first byte of the requested

descriptor. The descriptor RAM is 1024 bytes deep.

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

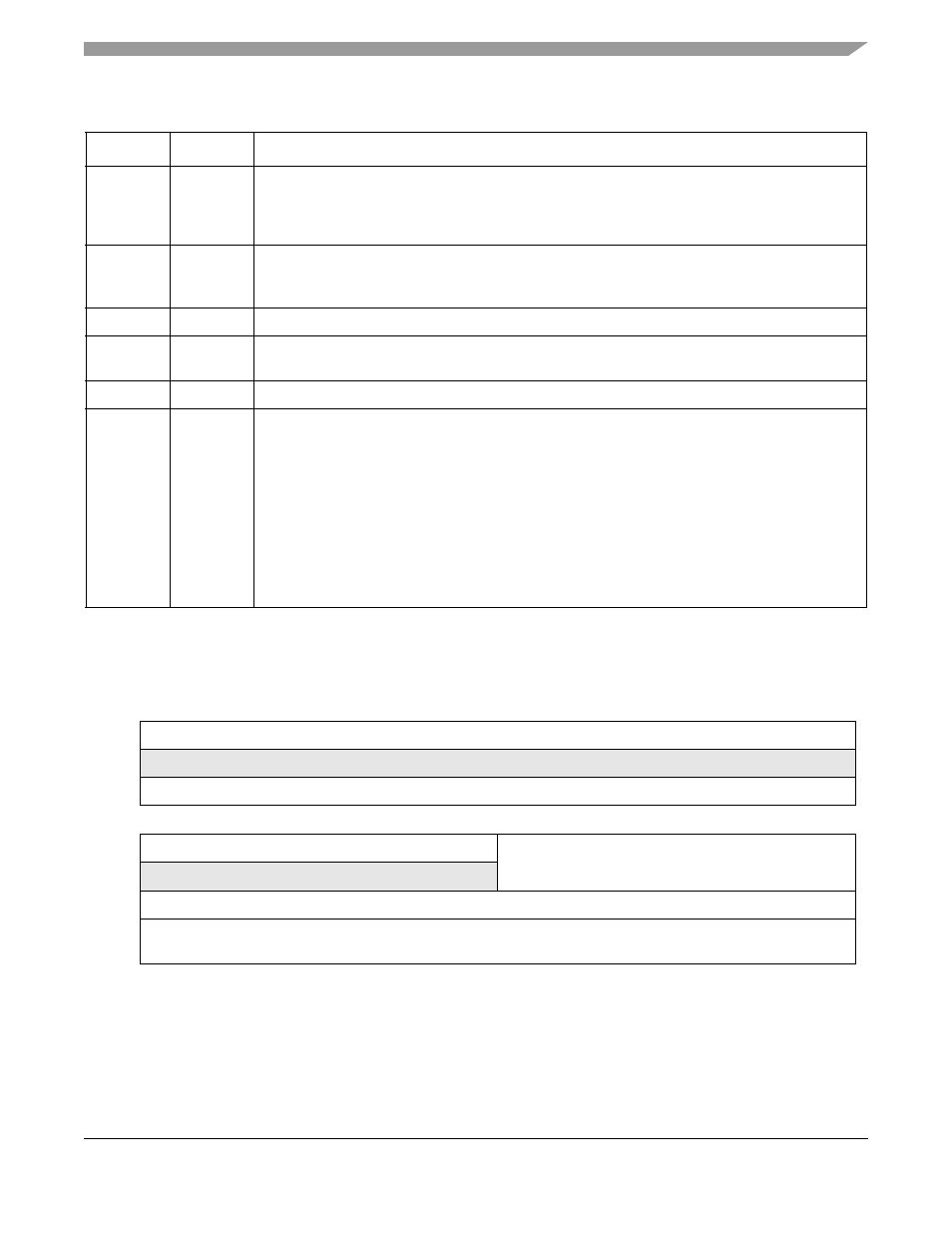

R

Uninitialized

W

Reset

Uninitialized

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

R

Uninitialized

DDAT

W

Reset

Uninitialized

Reg

Addr

MBAR + 0xB40C

Figure 29-5. USB Descriptor RAM Data Register (DRAMDR)