Freescale Semiconductor MCF5480 User Manual

Page 192

MCF548x Reference Manual, Rev. 3

6-2

Freescale Semiconductor

describes addressing modes and syntax for floating-point instructions.

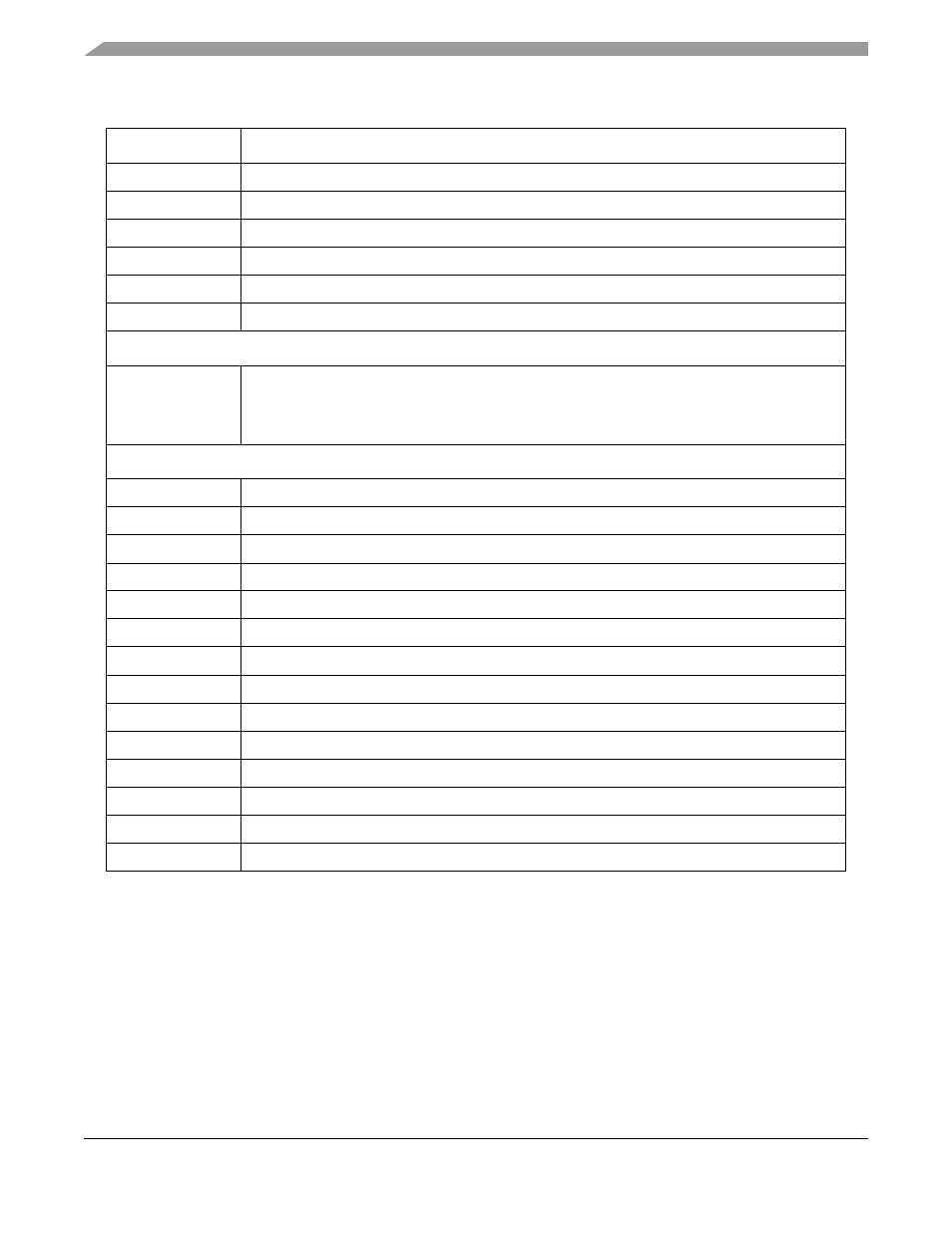

&

Logical AND

|

Logical OR

→

Source operand is moved to destination operand

Any double-operand operation

Operand is compared to zero and the condition codes are set appropriately

sign-extended

All bits of the upper portion are made equal to the high-order bit of the lower portion

Other Operations

If

then

else

Test the condition. If true, the operations after then are performed. If the condition is false and the

optional else clause is present, the operations after else are performed. If the condition is false

and else is omitted, the instruction performs no operation. Refer to the Bcc instruction description

as an example.

Register Specifications

An

Address register n (example: A3 is address register 3)

Ay, Ax

Source and destination address registers, respectively

Dn

Data register n (example: D3 is data register 3)

Dy,Dx

Source and destination data registers, respectively

FPCR

Floating-point control register

FPIAR

Floating-point instruction address register

FPn

Floating-point data register n (example: FP3 is FPU data register 3)

FPSR

Floating-point status register

FPy,FPx

Source and destination floating-point data registers, respectively

PC

Program counter

Rn

Address or data register

Rx

Destination register

Ry

Source register

Xi

Index register

Table 6-1. Notational Conventions (Continued)

Symbol

Description