Table 6-5, Describes fpsr fields – Freescale Semiconductor MCF5480 User Manual

Page 200

MCF548x Reference Manual, Rev. 3

6-10

Freescale Semiconductor

For AEXC[OVFL], AEXC[DZ], and AEXC[INEX], the next value is determined by ORing the current

AEXC value with the EXC equivalent, as shown in the following:

•

Next AEXC[OVFL] = Current AEXC[OVFL] | EXC[OVFL]

•

Next AEXC[DZ] = Current AEXC[DZ] | EXC[DZ]

•

Next AEXC[INEX] = Current AEXC[INEX] | EXC[INEX]

For AEXC[IOP] and AEXC[UNFL], the next value is calculated by ORing the current AEXC value with

EXC bit combinations, as follows:

•

Next AEXC[IOP] = Current AEXC[IOP] | EXC[BSUN | INAN | OPERR]

•

Next AEXC[UNFL] = Current AEXC[UNFL] | EXC[UNFL

& INEX]

6.3.4

Floating-Point Instruction Address Register (FPIAR)

The ColdFire OEP can execute integer and floating-point instructions simultaneously. As a result, the PC

value stacked by the processor in response to a floating-point exception trap may not point to the

instruction that caused the exception.

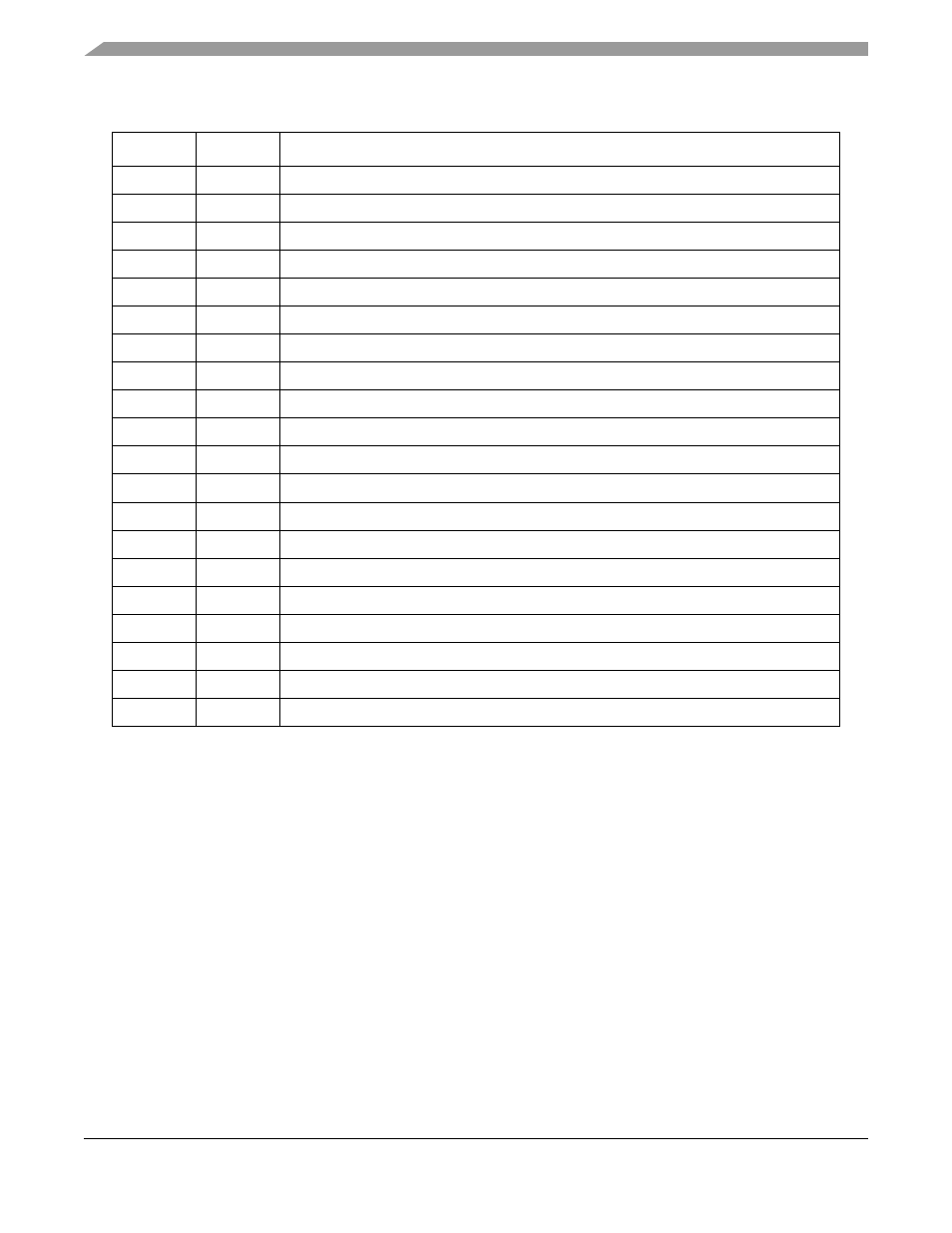

Table 6-5. FPSR Field Descriptions

Bits

Field

Description

31–28

—

Reserved, should be cleared.

27

N

Negative

26

Z

Zero

25

I

Infinity

24

NAN

Not-a-number

23–16

—

Reserved, should be cleared.

15

BSUN

Branch/set on unordered

14

INAN

Input not-a-number

13

OPERR

Operand error

12

OVFL

Overflow

11

UNFL

Underflow

10

DZ

Divide by zero

9

INEX

Inexact result

8

IDE

Input is denormalized

7

IOP

Invalid operation

6

OVFL

Overflow

5

UNFL

Underflow

4

DZ

Divide by zero

3

INEX

Inexact result

2–0

—

Reserved, should be cleared.