7 sec master control register (smcr), Sec master control register (smcr) -17, P. 22-17 – Freescale Semiconductor MCF5480 User Manual

Page 619

Controller

MCF548x Reference Manual, Rev. 3

Freescale Semiconductor

22-17

22.6.4.7

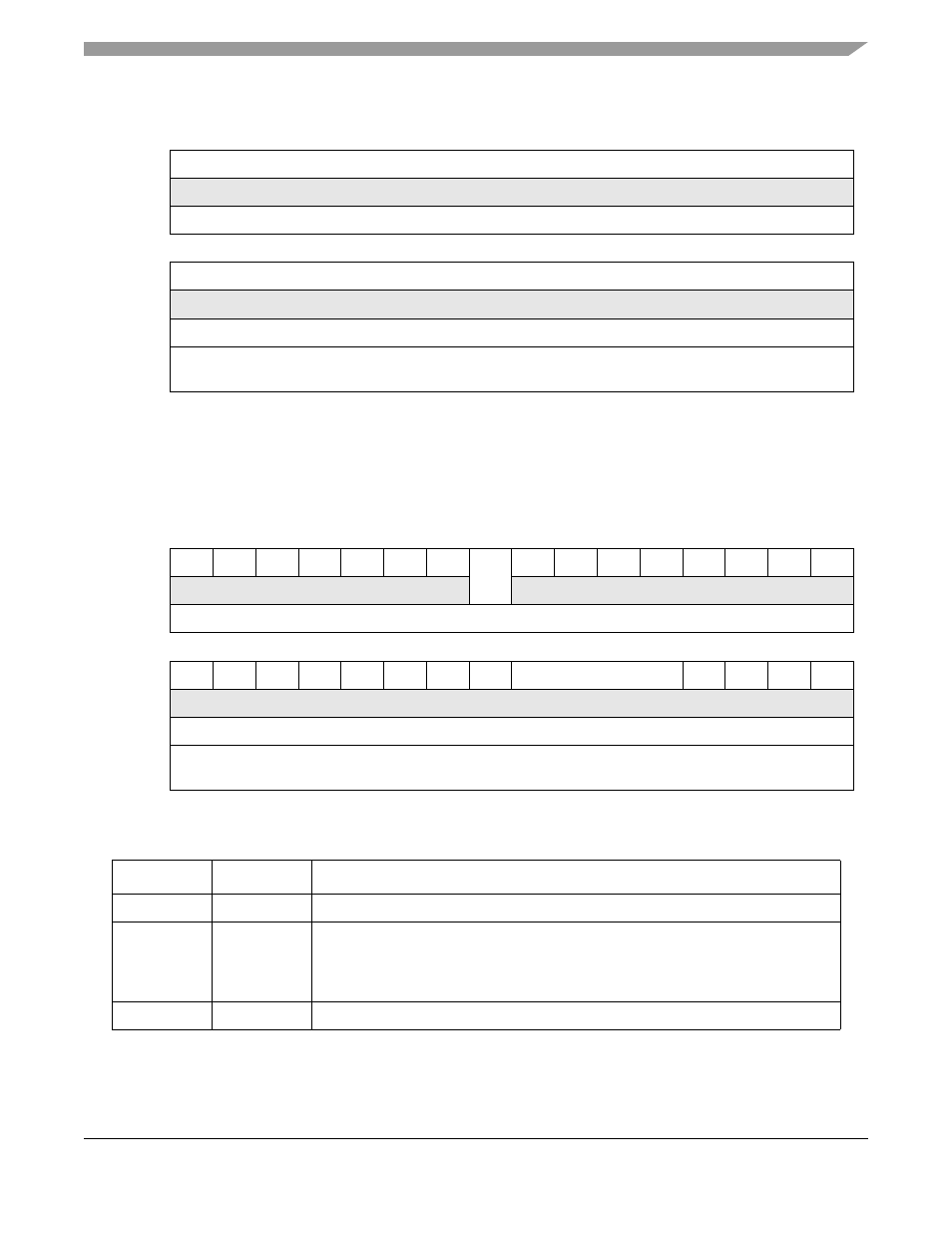

SEC Master Control Register (SMCR)

The SEC master control register (SMCR), shown in

, controls certain functions in the

controller and provides a means for software to reset the SEC.

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

R

Version

W

Reset

0

0

0

0

1

0

0

1

0

0

0

0

0

0

0

0

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

R

Version

W

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Reg

Addr

MBAR + 0x 21020

Figure 22-13. ID Register (SIDR)

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

R

0

0

0

0

0

0

0

SWR

0

0

0

0

0

0

0

0

W

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

R

0

0

0

0

0

0

0

0

CURR_CHAN

0

0

0

0

W

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Reg

Addr

MBAR + 0x 21030

Figure 22-14. SEC Master Control Register (SMCR)

Table 22-9. SMCR Field Descriptions

Bits

Name

Description

31–25

—

Reserved

24

SWR

Software Reset. Writing 1 to this bit will cause a global software reset. Upon

completion of the reset, this bit will be automatically cleared.

0 Don’t reset

1 Global Reset

23–8

—

Reserved