Freescale Semiconductor MCF5480 User Manual

Page 50

MCF548x Reference Manual, Rev. 3

l

Freescale Semiconductor

Add column to indicate whether the signal has a pull-up resistor.

These signals have a pull-up resistor at all times:

DSCLK/TRST, BKPT/TMS, DSI/TDI

These signals have a pull-up resistor whenever configured for general-purpose input (default state after

reset):

PCIBR[4:3], PCIGNT[4:3], E1MDIO, E1MDC, E1TXCLK, E1TXEN, E1TXD[3:0], E1COL, E1RXCLK,

E1RXDV, E1RXD[3:0], E1CRS, E1TXER, E1RXER

Remove overbars from the following signals: FBADDR1, FBADDR0, SDDATA, SDADDR, SDBA, TIN3,

TOUT3

In entry AD6, remove overbar from ALE and change description from “Transfer start” to “Address latch

enable”

Add overbars to IRQ[6:5].

• Replace PPSCLn entries under the GPIO column with PPSC1PSC0n. There is no PPSCL port.

• Replace PPSCHn entries under the GPIO column with PPSC3PSC2n. There is no PPSCH port.

The GPIO bit number for each of the UART control signals are incorrect for Table 2-2. However, they are

correct for Table 2-1:

• Y23/PSC1RTS pin: Change GPIO entry from PPSCL7 to PPSC1PSC06.

• AB23/PSC3RTS pin: Change GPIO entry from PPSCH7 to PPSC3PSC26.

• AB26/PSC0RTS pin: Change GPIO entry from PPSCL3 to PPSC1PSC02.

• AC19/PSC2CTS pin: Change GPIO entry from PPSCH2 to PPSC3PSC23.

• AD26/PSC2RTS pin: Change GPIO entry from PPSCH3 to PPSC3PSC22.

• AE23/PSC0CTS pin: Change GPIO entry from PPSCL2 to PPSC1PSC03.

• AF23/PSC3CTS pin: Change GPIO entry from PPSCH6 to PPSC3PSC27.

• AF25/PSC1CTS pin: Change GPIO entry from PPSCL6 to PPSC1PSC07.

Remove overbars from the following signals: IVDD, TCK, PLLVDD, PSTDDATA1, PSTDDATA7, SDDATA21,

PSTDDATA2, E1RXCLK, E1RXD2, SDVDD, SDDATA31, SDADDR4, DSCLK, VSS, EVDD, PCIAD29,

PCIAD30, SCL, SDDATA16, AD17, AD20, E1CRS, E0TXD2, TOUT2, TOUT1, PSC2TXD, ALE, E0TXD3,

SDBA1, SDBA0, USBVDD, PSC3RXD, AD25, USBRBIAS, TIN1, TIN2, TIN0

Add overbars to the following signals: IRQ3, IRQ2

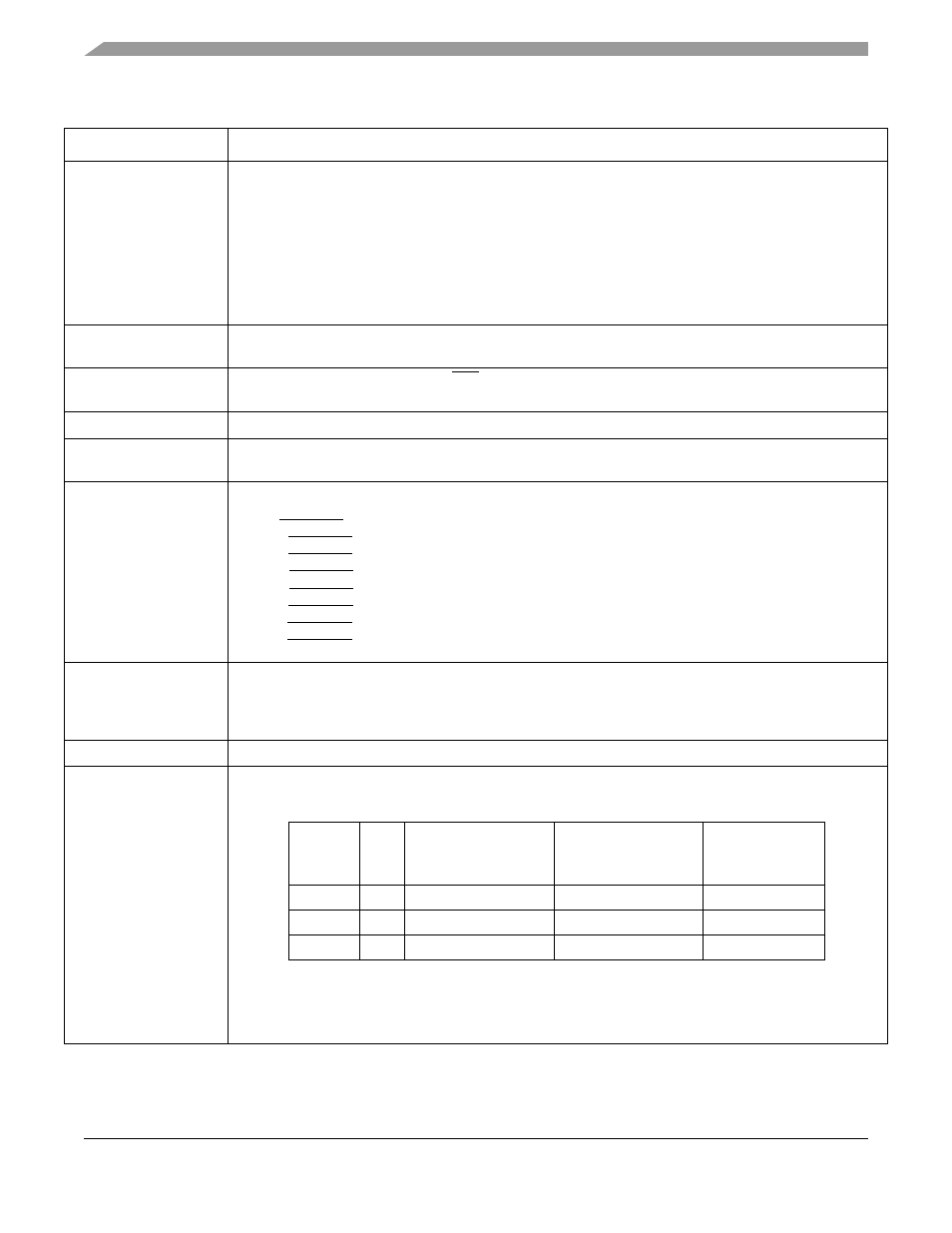

Replace table with the following:

Table iv. MCF548x Revision History (continued)

Section/Page

Substantive Changes

Table 1. MCF548x Divide Ratio Encodings

AD[12:8]

1

1

All other values of AD[12:8] are reserved.

Clock

Ratio

CLKIN–PCI and FlexBus

Frequency Range (MHz)

Internal XLB, SDRAM

bus, and PSTCLK

Frequency Range (MHz)

Core Frequency

Range (MHz)

00011

1:2

41.6–50.0

83.33–100

166.66–200

00101

1:2

25.0–41.5

50.0–83.0

2

2

Note that DDR memories typically have a minimum speed of 83 MHz. Some vendors specifiy

down to 75 MHz. Check with the memory component specifications to verify.

100.0–166.66

01111

1:4

25.0

100

200