Freescale Semiconductor MCF5480 User Manual

Page 218

MCF548x Reference Manual, Rev. 3

6-28

Freescale Semiconductor

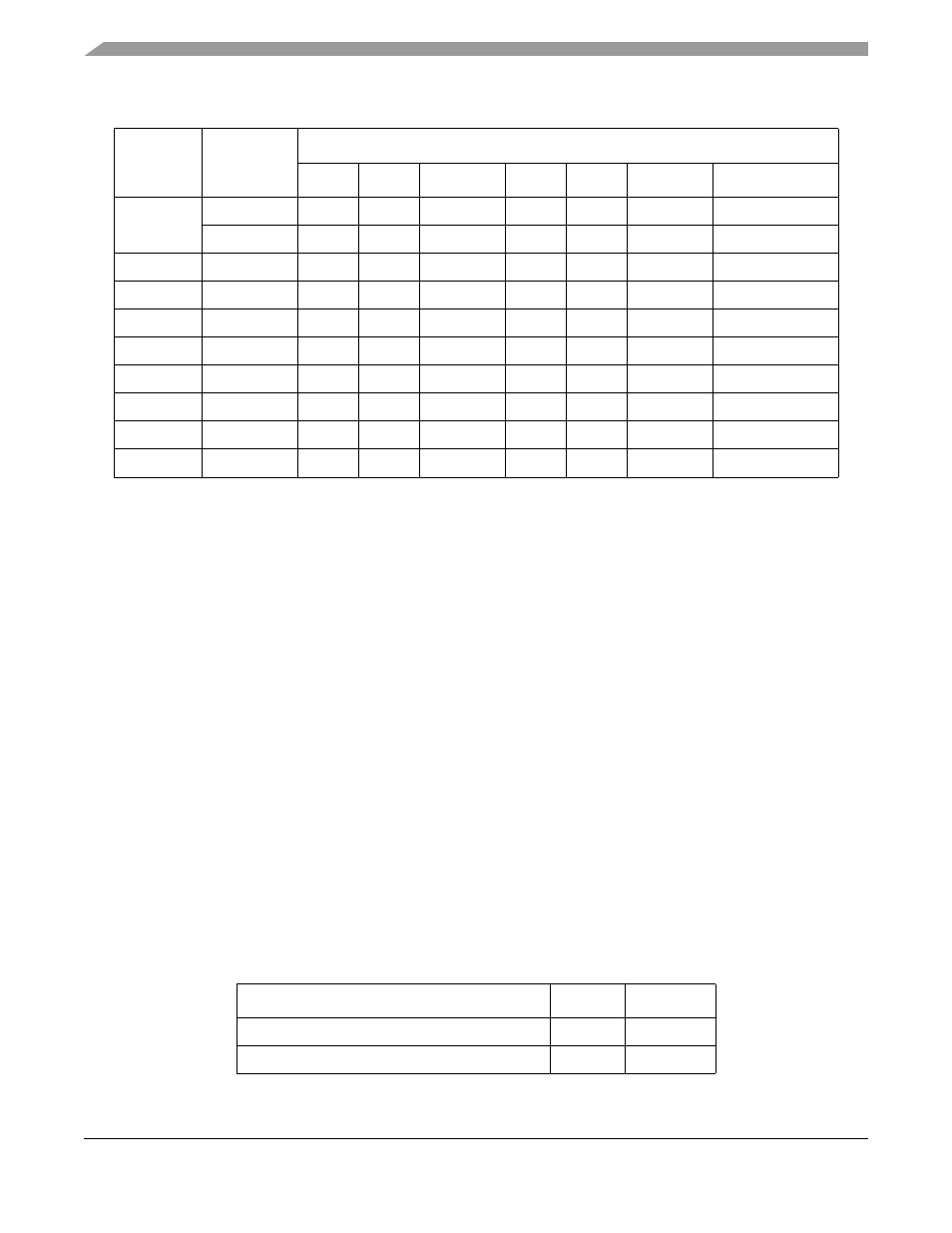

The ColdFire architecture supports concurrent execution of integer and floating-point instructions. The

latencies in this table define the execution time needed by the FPU. After a multi-cycle FPU instruction is

issued, subsequent integer instructions can execute concurrently with the FPU execution. For this

sequence, the floating-point instruction occupies only one OEP cycle.

6.7.3

Key Differences between ColdFire and M68000 FPU Programming

Models

This section is intended for compiler developers and developers porting assembly language routines from

the M68000 family to ColdFire. It highlights major differences between the ColdFire FPU instruction set

architecture (ISA) and the equivalent M68000 family ISA, using the MC68060 as the reference. The

internal FPU datapath width is the most obvious difference. ColdFire uses 64-bit double-precision and the

M68000 family uses 80-bit extended precision. Other differences pertain to supported addressing modes,

both across all FPU instructions as well as specific opcodes.

lists key differences. Because all

ColdFire implementations support instruction sizes of 48 bits or less, M68000 operations requiring larger

instruction lengths cannot be supported.

.

FMOVEM

4

—

—

2n(2n/0)

—

—

2n(2n/0)

2n(2n/0)

#list,

—

—

1+2n(0/2n)

—

—

1+2n(0/2n)

—

FMUL

4(0/0)

4(0/0)

4(1/0)

4(1/0)

4(1/0)

4(1/0)

4(1/0)

FNEG

1(0/0)

1(0/0)

1(1/0)

1(1/0)

1(1/0)

1(1/0)

1(1/0)

FNOP

—

—

—

—

—

—

2(0/0)

FRESTORE

—

—

6(4/0)

—

—

6(4/0)

6(4/0)

FSAVE

—

—

7(0/4)

—

—

7(0/4)

—

FSQRT

56(0/0)

56(0/0)

56(1/0)

56(1/0)

56(1/0)

56(1/0)

56(1/0)

FSUB

4(0/0)

4(0/0)

4(1/0)

4(1/0)

4(1/0)

4(1/0)

4(1/0)

FTST

1(0/0)

1(0/0)

1(1/0)

1(1/0)

1(1/0)

1(1/0)

1(1/0)

1

Add 1(1/0) for an external read operand of double-precision format for all instructions except FMOVEM, and 1(0/1)

for FMOVE FPy,

2

If the external operand is an integer format (byte, word, longword), there is a 4 cycle conversion time which must be

added to the basic execution time.

3

If any exceptions are enabled, the execution time for FMOVE FPy,

exception is enabled, the execution time for FBcc increases by one cycle.

4

For FMOVEM, n refers to the number of registers being moved.

Table 6-26. Key Programming Model Differences

Feature

M68000

ColdFire

Internal datapath width

80 bits

64 bits

Support for fpGEN d

8

(An,Xi),FPx

Yes

No

Table 6-25. Floating-Point Instruction Execution Times

1,

2,

3

(Continued)

Opcode

Format

Effective Address

FPn

Dn

(An)

(An)+

-(An)

(d

16

,An)

(d

16

,PC)