3 arbitration latency, 4 arbitration examples, Arbitration latency -7 – Freescale Semiconductor MCF5480 User Manual

Page 567: Arbitration examples -7

Functional Description

MCF548x Reference Manual, Rev. 3

Freescale Semiconductor

20-7

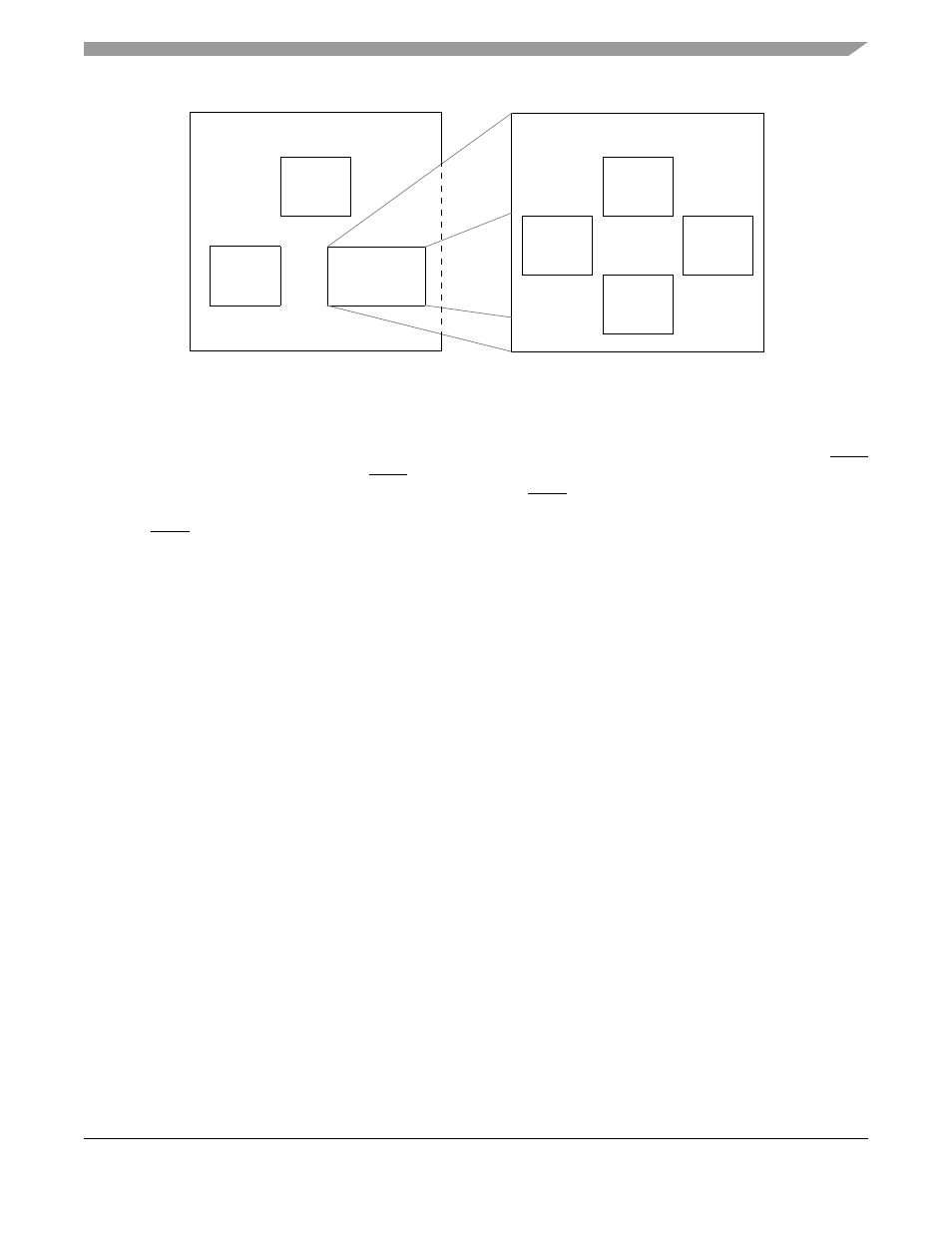

Figure 20-4. PCI Arbitration Initial State

20.4.2.3

Arbitration Latency

Worst case arbitration latency: arbitration latency is the number of clock cycles from a master’s REQ

assertion to PCI bus idle state AND its GNT assertion. In a lightly loaded system, arbitration latency would

be the time it takes for the bus arbiter to assert the master’s GNT (zero cycles if the arbiter is parked with

the requesting master and two if parked with another master). If a transaction is in progress when the

master’s GNT is asserted, the master must wait for the current transaction to complete and any subsequent

transactions from higher priority requesting masters. In a situation where there are multiple requesting

masters, each master’s tenure on the bus is limited by its master latency timer.

20.4.2.4

Arbitration Examples

shows basic arbitration. Three master devices are used to illustrate how an arbiter may

alternate bus accesses. (Assume device 0, device 1, and device 2 are assigned the same priority group and

no other masters are requesting use of the bus.)

High-Priority Group

MCF548X

(1/3)

Device 1

(1/3)

Low-Priority Group

Device 2

(1/12)

Low-Priority

Group Slot

(1/3)

Device 4

(1/12)

Device 0

(1/12)

Device 3

(1/12)

3a

1a

2a

1b

3b

4b

2b

PCI Arbiter Control Register PACR[26:31] = 000101b