6 usb endpoint n fifo status register (epnfsr), Usb endpoint, 6 usb endpoint n fifo status register (ep n fsr) – Freescale Semiconductor MCF5480 User Manual

Page 914

MCF548x Reference Manual, Rev. 3

29-40

Freescale Semiconductor

29.2.5.6

USB Endpoint n FIFO Status Register (EPnFSR)

Table 29-40. EPnFDR Field Descriptions

Bits

Name

Description

31–0

TXDATA

This is the transmit FIFO write data

31–0

RXDATA

This is the receive FIFO read data

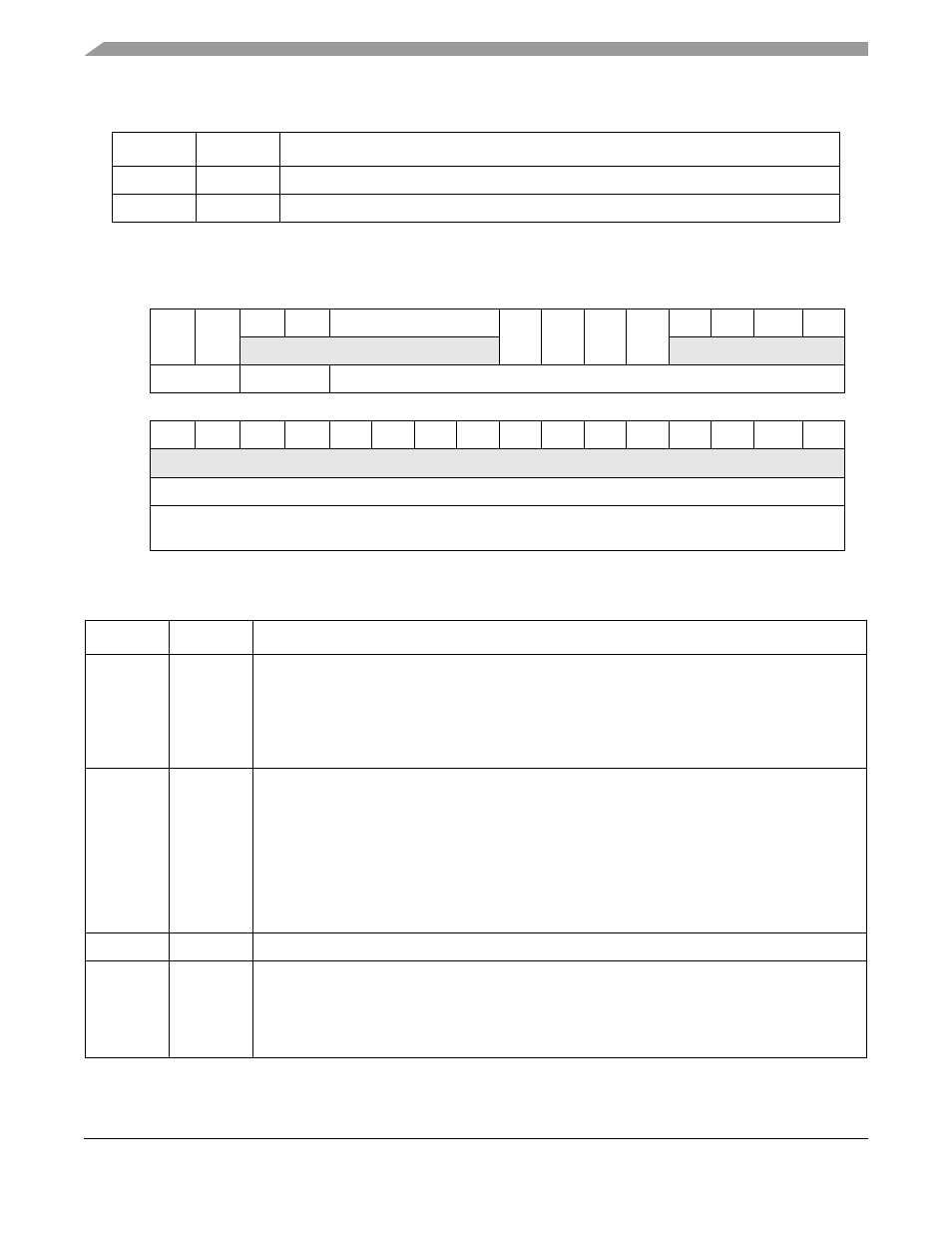

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

R

IP

TXW

0

0

FRM

FAE

RXW

UF

OF

FR

FU

ALRM EMT

W

Reset

0

0

Uninitialized

0

0

0

0

0

0

0

0

0

0

0

1

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

R

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

W

Reset

Uninitialized

Reg

Addr

MBAR + 0xB454 (EP0FSR); 0xB484 (EP1FSR); 0xB4B4 (EP2FSR); 0xB4E4 (EP3FSR);

0xB514 (EP4FSR); 0xB544 (EP5FSR); 0xB574 (EP6FSR)

Figure 29-46. USB Endpoint n FIFO Status Register (EPnFSR)

Table 29-41. EPnFSR Field Descriptions

Bits

Name

Description

31

IP

Illegal pointer. This bit signifies an illegal pointer condition in the FIFO controller. The assertion of

this bit will cause a FIFO error condition (ERR) in the

EPnISR

unless the EPnFCR[IPMSK] bit is

set. This bit will remain set until a one is written to this bit location.

0 No illegal pointer condition.

1 An address outside the FIFO controller’s memory range has been written to one of the

user-visible pointers.

30

TXW

Transmit wait states. This bit indicates that the current IN (transmit) transaction from the USB is

incurring wait states because there is not enough data in the FIFO to satisfy the read request. Even

though the FIFO is not in a catastrophic state (i.e., normal operation can proceed without flushing

the FIFO), this may result in an inadvertent short packet being transmitted for the current IN

transaction.

The assertion of this bit will cause a FIFO error condition (ERR) in the EPnISR unless the TXWMSK

bit in the EPnFCR is set. This bit will remain set until a one is written to this bit location.

0 No transmit wait condition.

1 Transmit wait condition.

29–28

—

Reserved, should be cleared.

27–24

FRM

Frame indicator. This bus provides a frame status indicator for non-DMA applications.

1000 A frame boundary has occurred on the [31:24] byte of the data bus

0100 A frame boundary has occurred on the [23:16] byte of the data bus

0010 A frame boundary has occurred on the [15:8] byte of the data bus

0001 A frame boundary has occurred on the [7:0] byte of the data bus