4 functional description, 1 timer configuration method, 2 programming notes – Freescale Semiconductor MCF5480 User Manual

Page 348: Functional description -8, Timer configuration method -8, Programming notes -8

MCF548x Reference Manual, Rev. 3

11-8

Freescale Semiconductor

11.4

Functional Description

11.4.1

Timer Configuration Method

Use the following method to configure each timer:

1. Determine the mode select field (GMSn[TMS]) value for the desired operation.

2. Program any other registers associated with this mode.

3. Program interrupt enable as desired.

4. Enable the timer by writing the mode select value into the TMS field.

11.4.2

Programming Notes

Programmers should observe the following notes:

1. Intermediate values of the timer internal counters are not readable by software.

2. In PWM mode, an interrupt occurs at the beginning of a pulse. An interrupt service routine

prepares the new pulse width of the next pulse while the current pulse is running.

3. The stop/continuous mode bit (GMSn[SC] ) operates differently for different modes. In general,

this bit controls whether the timer halts at the end of a current mode, or resets and continues with

a repetition of the mode. See

for precise operation.

4. The GMSn[TMS] field operates somewhat as a global enable. If it is zero, then all timer modes

are disabled and internal counters are reset. See

5. There is a counter enable bit (GMSn[CE]) that operates somewhat independently of the TMS

field. This bit controls the counter for CPU timer or watchdog timer modes only. See

to understand the operation of these bits across the various modes.

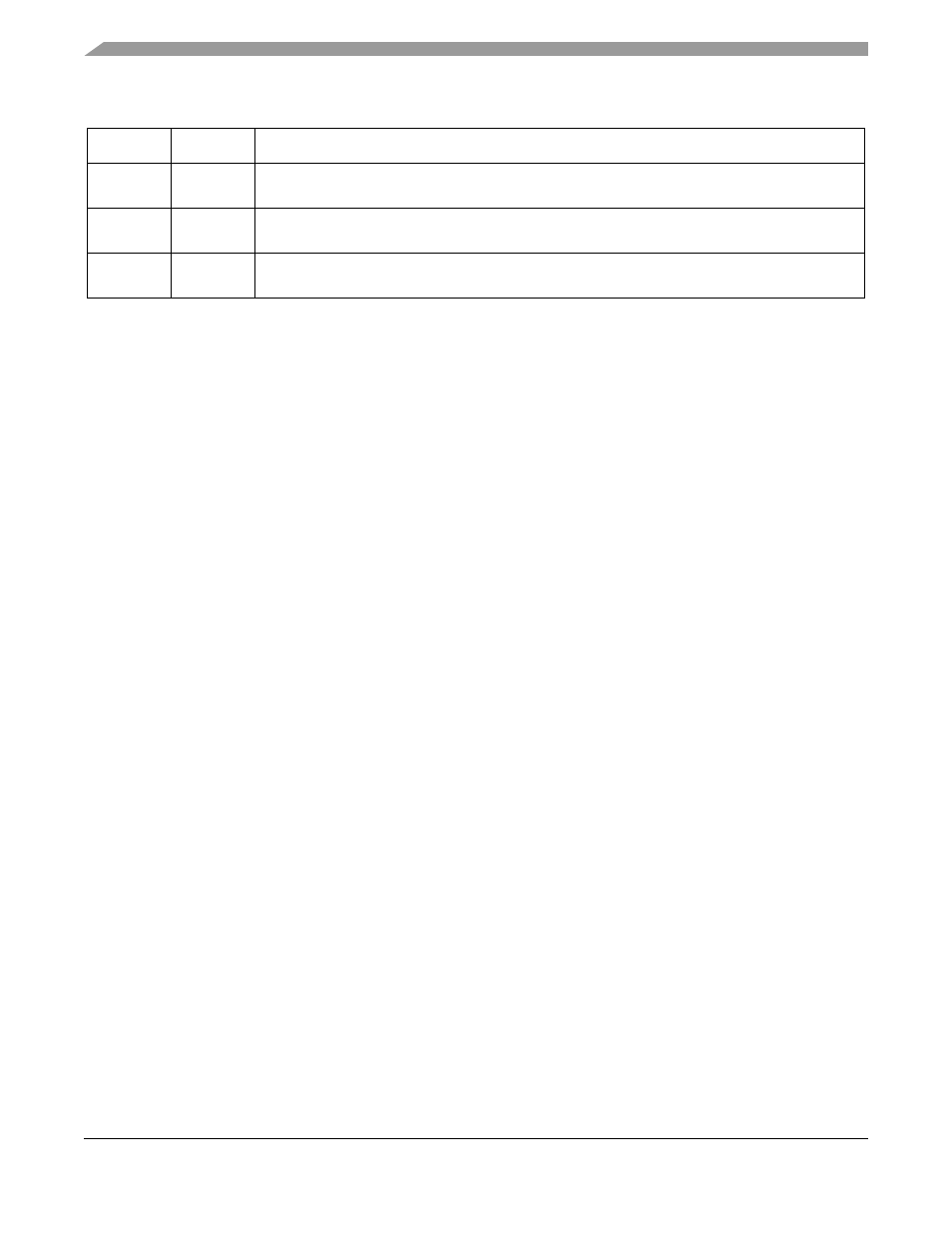

2

PWMP

PWM end of period occurred. Cleared by writing 1 to this bit position. Also cleared if TMS is 000

(i.e., timer not enabled).

1

COMP

OC reference event occurred. Cleared by writing 1 to this bit position. Also cleared if TMS is 000

(i.e., timer not enabled).

0

CAPT

IC reference event occurred. Cleared by writing 1 to this bit position. Also cleared if TMS is 000

(i.e., timer not enabled).

Table 11-5. GSRn Field Descriptions (Continued)

Bits

Name Description