Freescale Semiconductor MCF5480 User Manual

Page 48

MCF548x Reference Manual, Rev. 3

xlviii

Freescale Semiconductor

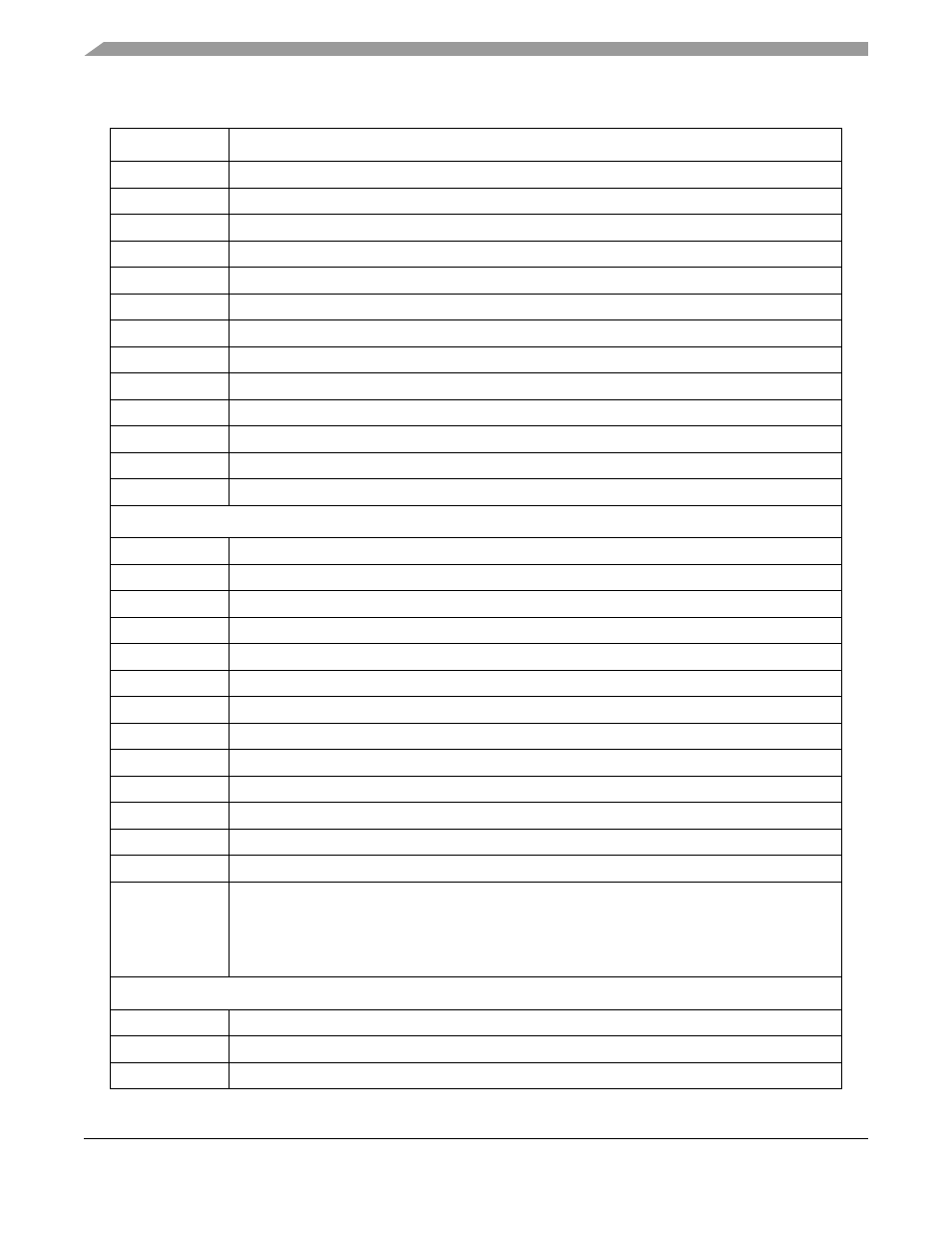

Source and destination effective addresses, respectively

Assembly language program label

List of registers for MOVEM instruction (example: D3–D0)

Shift operation: shift left (<<), shift right (>>)

Operand data size: byte (B), word (W), longword (L)

bc

Both instruction and data caches

dc

Data cache

ic

Instruction cache

#

Identifies the 4-bit vector number for trap instructions

<>

identifies an indirect data address referencing memory

identifies an absolute address referencing memory

dn

Signal displacement value, n bits wide (example: d16 is a 16-bit displacement)

SF

Scale factor (x1, x2, x4 for indexed addressing mode, <<1n>> for MAC operations)

Operations

+

Arithmetic addition or postincrement indicator

–

Arithmetic subtraction or predecrement indicator

x

Arithmetic multiplication

/

Arithmetic division

~

Invert; operand is logically complemented

&

Logical AND

|

Logical OR

^

Logical exclusive OR

<<

Shift left (example: D0 << 3 is shift D0 left 3 bits)

>>

Shift right (example: D0 >> 3 is shift D0 right 3 bits)

→

Source operand is moved to destination operand

←→

Two operands are exchanged

sign-extended

All bits of the upper portion are made equal to the high-order bit of the lower portion

If

then

else

Test the condition. If true, the operations after ‘then’ are performed. If the condition is false and the

optional ‘else’ clause is present, the operations after ‘else’ are performed. If the condition is false

and else is omitted, the instruction performs no operation. Refer to the Bcc instruction description

as an example.

Subfields and Qualifiers

{}

Optional operation

()

Identifies an indirect address

d

n

Displacement value, n-bits wide (example: d

16

is a 16-bit displacement)

Table iii. Notational Conventions (continued)

Instruction

Operand Syntax