Freescale Semiconductor MCF5480 User Manual

Page 75

Introduction

MCF548x Reference Manual, Rev. 3

Freescale Semiconductor

2-5

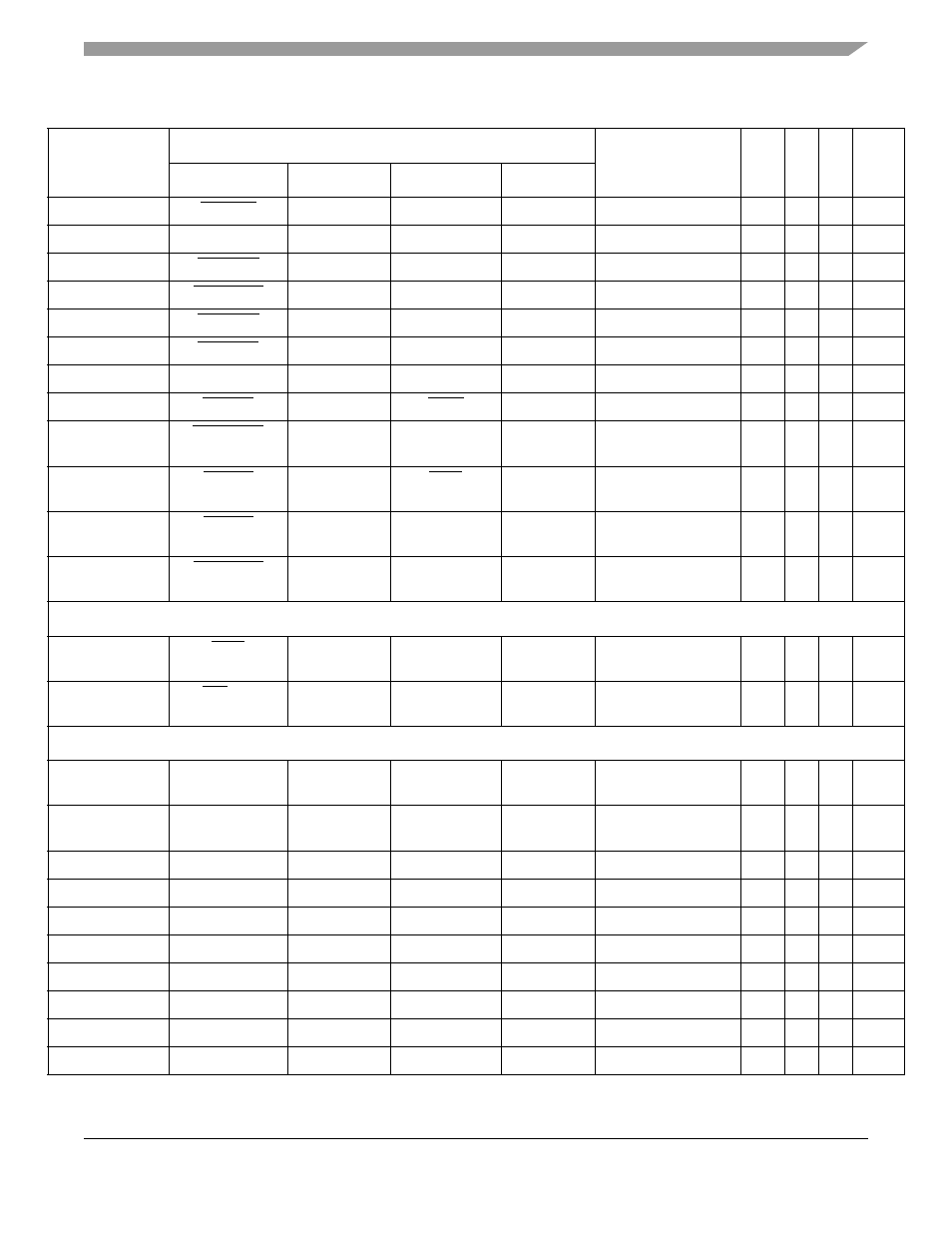

D24

PCIIRDY

—

—

—

PCI initiator ready

I/O

16

Hi-Z

F23

PCIPAR

—

—

—

PCI parity

I/O

16

Hi-Z

D26

PCIPERR

—

—

—

PCI parity error

I/O

16

Hi-Z

G23

PCIRESET

—

—

—

PCI reset

O

16

Low

F24

PCISERR

—

—

—

PCI system error

I/O

16

Hi-Z

E25

PCISTOP

—

—

—

PCI stop

I/O

16

Hi-Z

C26

PCITRDY

—

—

—

PCI target ready

I/O

16

Hi-Z

W24

PCIBG4

PPCIBG4

TBST

—

PCI external grant 4

O:I/O

16

GPI

Y26, W25, V24,

W26

PCIBG[3:0]

PPCIBG[3:0]

TOUT[3:0]

—

PCI external grant 3–0 O:I/O

16

GPI

D21

PCIBR4

PPCIBR4

IRQ4

—

PCI external

request 4

I:I/O

Y

1

8

GPI

B24

PCIBR3

PPCIBR3

TIN3

—

PCI external

request 3

I:I/O

Y

8

GPI

A25, B23, A24

PCIBR[2:0]

PPCIBR[2:0]

TIN[2:0]

—

PCI external

request 2–0

I:I/O

8

GPI

External Interrupts Port

D14

IRQ7

PIRQ7

—

—

External interrupt

request 7

I:I/O

—

—

B14, A14

IRQ[6:5]

PIRQ[6:5]

CANRX1

—

External interrupt

request 6–5

I:I/O

—

—

Ethernet MAC 0

AF10

E0MDIO

PFECI2C3

—

—

Management channel

serial data

I/O

8

GPI

AD11

E0MDC

PFECI2C2

—

—

Management channel

clock

O:I/O

8

GPI

AF9

E0TXCLK

PFEC0H7

—

—

MAC transmit clock

I:I/O

8

GPI

AE10

E0TXEN

PFEC0H6

—

—

MAC transmit enable

O:I/O

8

GPI

AD9

E0TXD0

PFEC0H5

—

—

MAC transmit data

O:I/O

8

GPI

AC9

E0COL

PFEC0H4

—

—

MAC collision

I:I/O

8

GPI

AD14

E0RXCLK

PFEC0H3

—

—

MAC receive clock

I:I/O

8

GPI

AE14

E0RXDV

PFEC0H2

—

—

MAC receive enable

I:I/O

8

GPI

AD13

E0RXD0

PFEC0H1

—

—

MAC receive data

I:I/O

8

GPI

AE19

E0CRS

PFEC0H0

—

—

MAC carrier sense

I:I/O

8

GPI

Table 2-1. MCF548x Signal Description (Continued)

PBGA Pin

Pin Functions

Description

I/O

Pu

ll-u

p

Drive

Res

e

t

St

a

te

Primary

GPIO

Secondary

Tertiary