Table 30-41/30-42 – Freescale Semiconductor MCF5480 User Manual

Page 972

MCF548x Reference Manual, Rev. 3

30-42

Freescale Semiconductor

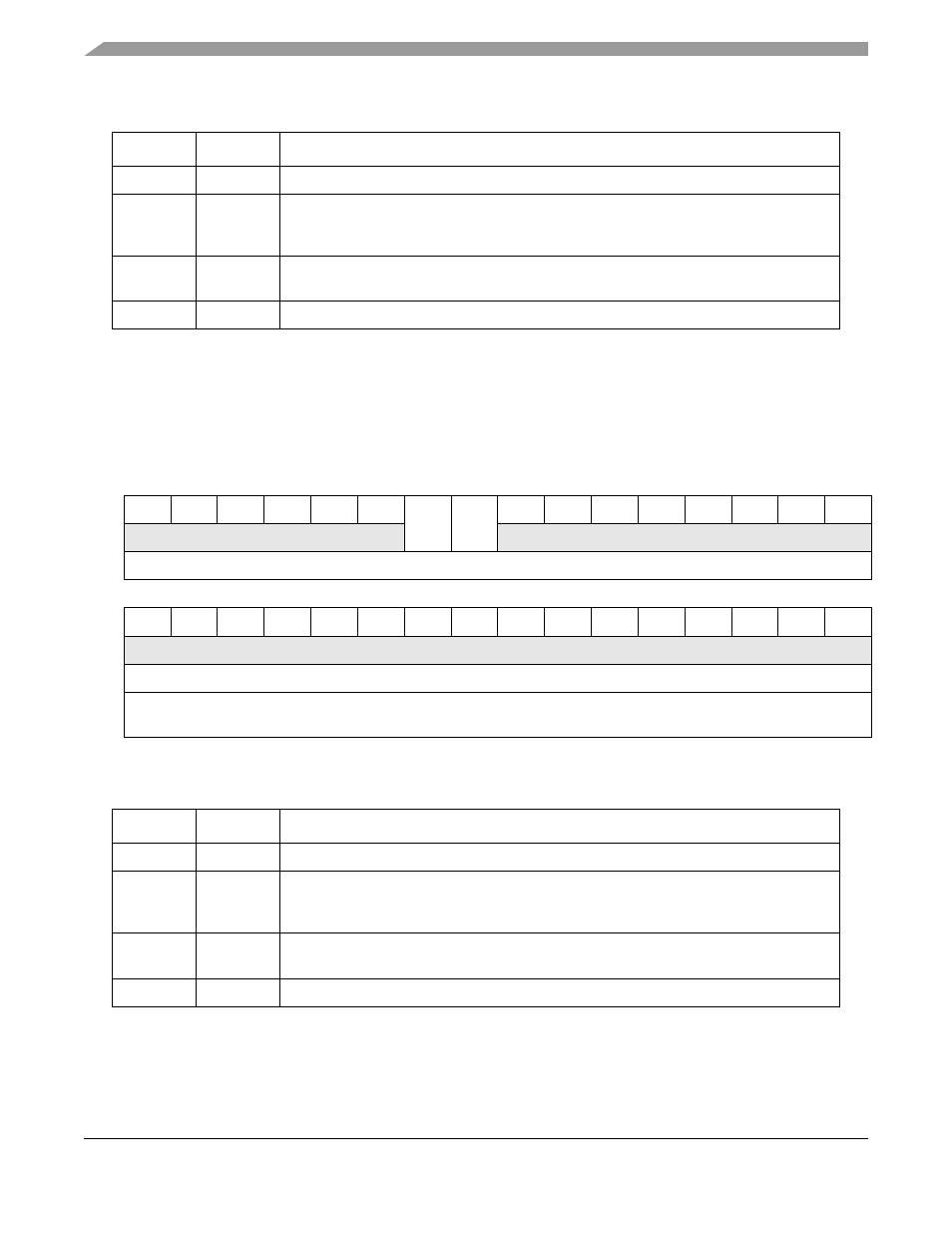

30.3.3.35 FEC CRC and Transmit Frame Control Word Register (FECCTCWR)

The FEC can be sent a control word (32-bit) with additional instructions on how to transmit the current

frame. This control word instructs the FEC to append or not append a CRC value to the frame being

transmitted. Control of the transmit frame control word and its contents are provided in this register.

Table 30-41. FECFRST Field Descriptions

Bits

Name

Descriptions

31–26

—

Reserved, should be cleared

25

SW_RST

Software Reset. This bit controls the soft reset of the FEC FIFOs. A soft reset will reset the

FIFO pointers and byte counters but notthe status and control registers. To cause a soft

reset this bit should be set and then cleared by application software.

24

RST_CTL

Reset control. Setting this bit allows the FEC controller to perform a soft reset of the FIFOs

when the FEC is disabled (ECR[ETHER_EN] cleared).

23–0

—

Reserved, should be cleared

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

R

0

0

0

0

0

0

CRC TFCW

0

0

0

0

0

0

0

0

W

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

R

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

W

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Reg

Addr

MBAR + 0x91C8 (FEC0), 0x99C8 (FEC1)

Figure 30-38. FEC CRC and Transmit Frame Control Word Register (FECCTCWR)

Table 30-42. FECCTCWR Field Descriptions

Bits

Name

Descriptions

31–26

—

Reserved, should be cleared

25

CRC

CRC enable. This bit is associated with the TC field in FEC’s Transmit Frame Control Word.

A 1 in this bit location translates to TC = 1 and instructs FEC to append CRC to the current

transmit frame.

24

TFCW

Transmit frame control word enable. This bit controls whether a “control word” is appended

to the frame being transferred to the transmit FIFO.

23–0

—

Reserved, should be cleared