2 register descriptions, 1 flexcan module configuration register (canmcr), Register descriptions -6 – Freescale Semiconductor MCF5480 User Manual

Page 576: Flexcan module configuration register (canmcr) -6

MCF548x Reference Manual, Rev. 3

21-6

Freescale Semiconductor

21.3.2

Register Descriptions

This section describes the registers in the FlexCAN module.

NOTE

The FlexCAN has no hard-wired protection against invalid bit/field

programming within its registers. Specifically, no protection is provided if

the programming does not meet CAN protocol requirements.

Programming the FlexCAN control registers is typically done during system initialization, prior to the

FlexCAN becoming synchronized with the CAN bus. The configuration registers can be changed after

synchronization by halting the FlexCAN module. This is done when the user sets the HALT bit in the

FlexCAN module configuration register (CANMCR). The FlexCAN responds by setting the

CANMCR[NOTRDY] bit. Additionally, the control registers can be modified while the MPU is in

background freeze mode.

21.3.2.1

FlexCAN Module Configuration Register (CANMCR)

CANMCR defines global system configurations, such as the module operation mode and maximum

message buffer configuration. Most of the fields in this register can be accessed at any time, except the

MAXMB field, which should only be changed while the module is in freeze mode.

0xA034–

0xA07F

0xA834–

0xA87F

Reserved

—

0xA080–

0xA17F

0xA880–

0xA97F

Message buffers 0–15

MB

S/U

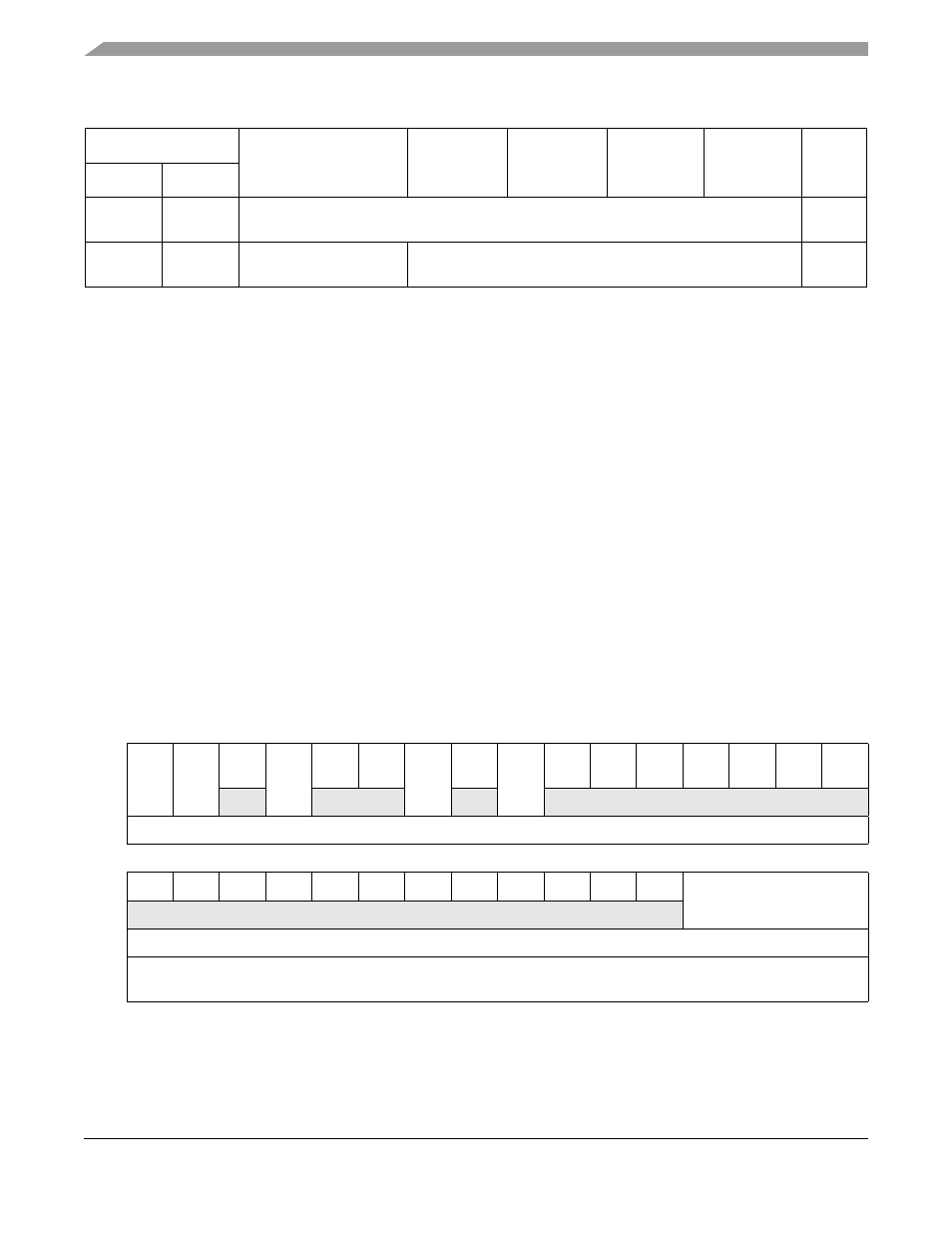

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

R MDIS

FRZ

0

HALT

0

0

SOFT

RST

FRZ

ACK

SUPV

0

0

0

0

0

0

0

W

1

1

0

1

1

0

0

0

1

0

0

1

0

0

0

0

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

R

0

0

0

0

0

0

0

0

0

0

0

0

MAXMB

W

Reset

0

0

0

0

0

0

0

0

0

0

0

0

1

1

1

1

Reg

Addr

MBAR + 0xA000 (CANMCR0); 0xA800 (CANMCR1)

Figure 21-4. FlexCAN Module Configuration Register (CANMCR)

Table 21-1. FlexCAN Memory Map (Continued)

MBAR Offset

Name

Byte0

Byte1

Byte2

Byte3

Access

FlexCAN0 FlexCAN1