1 slt terminal count register (stcntn), 2 slt control register (scrn), Slt terminal count register (stcntn) -2 – Freescale Semiconductor MCF5480 User Manual

Page 350: Slt control register (scrn) -2

MCF548x Reference Manual, Rev. 3

12-2

Freescale Semiconductor

12.2.1

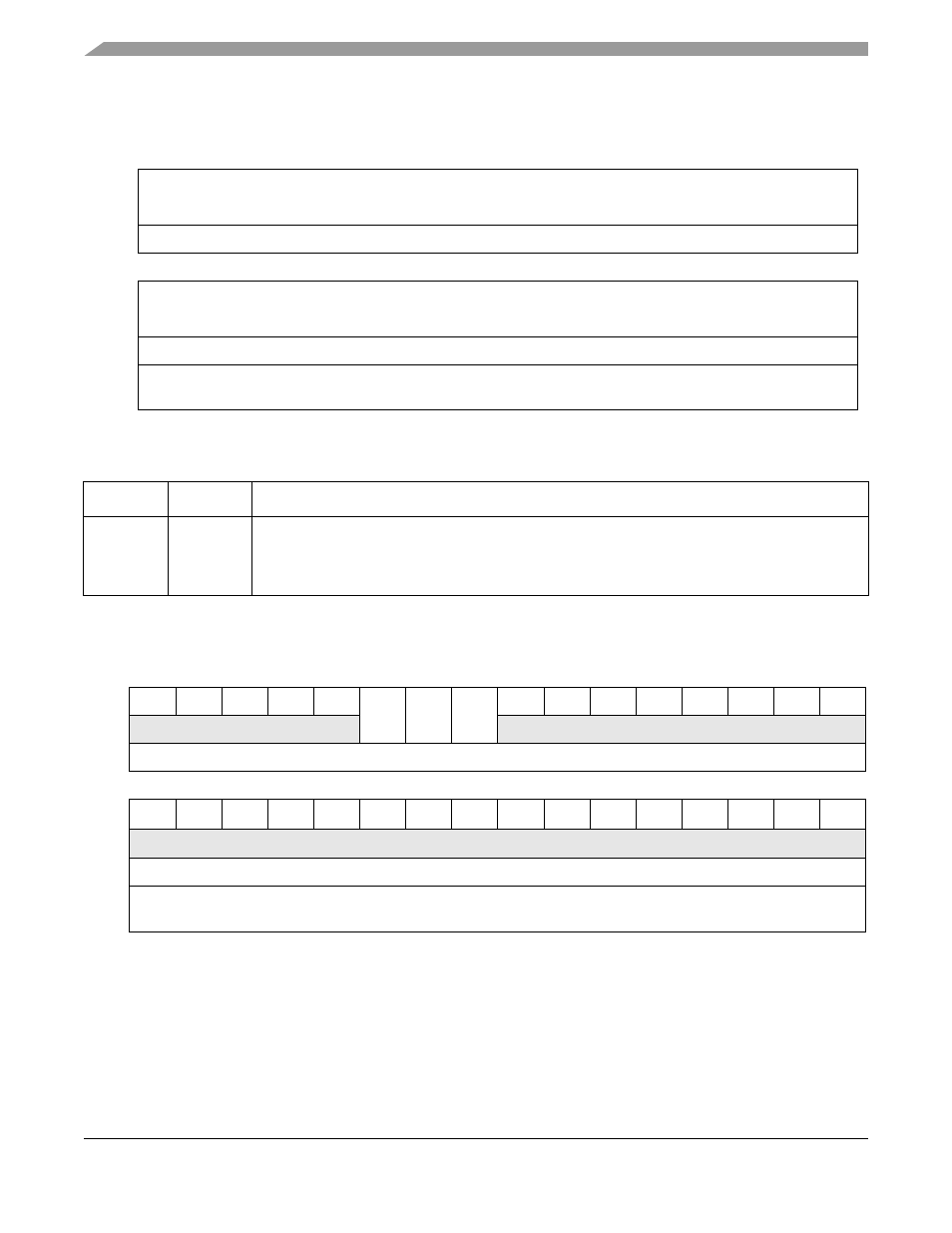

SLT Terminal Count Register (STCNTn)

12.2.2

SLT Control Register (SCRn)

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

R

TC

W

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

R

TC

W

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Reg

Addr

MBAR + 0x900 (STCNT0), + 0x910 (STCNT1)

Figure 12-1. SLT Terminal Count Register (STCNTn)

Table 12-2. STCNTn Field Descriptions

Bits

Name Description

31–0

TC

Terminal count. GPIO output bit set. The user programs this register to set the terminal count value

to be used by the SLT. This register can be updated even if the timer is running; the new value takes

effect immediately. The new value also clears any existing interrupt.

Note: Software should not write a value less than 255 to the timer.

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

R

0

0

0

0

0

RUN

IEN

TEN

0

0

0

0

0

0

0

0

W

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

R

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

W

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Reg

Addr

MBAR + 0x904 (SCR0), + 0x914 (SCR1)

Figure 12-2. SLT Control Register (SCRn)