Freescale Semiconductor MCF5480 User Manual

Page 334

MCF548x Reference Manual, Rev. 3

10-12

Freescale Semiconductor

to determine the state of the arbiter. It is possible that multiple conditions exist that would cause an

interrupt. Disabling an interrupt by writing a 0 to a bit in this register will not clear the status bit in the

arbiter status register.

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

R

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

W

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

R

0

0

0

0

0

0

0

SEAE MME

TTAE TTRE ECWE TTME

BAE

DTE

ATE

W

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Reg

Addr

MBAR + 0x024C

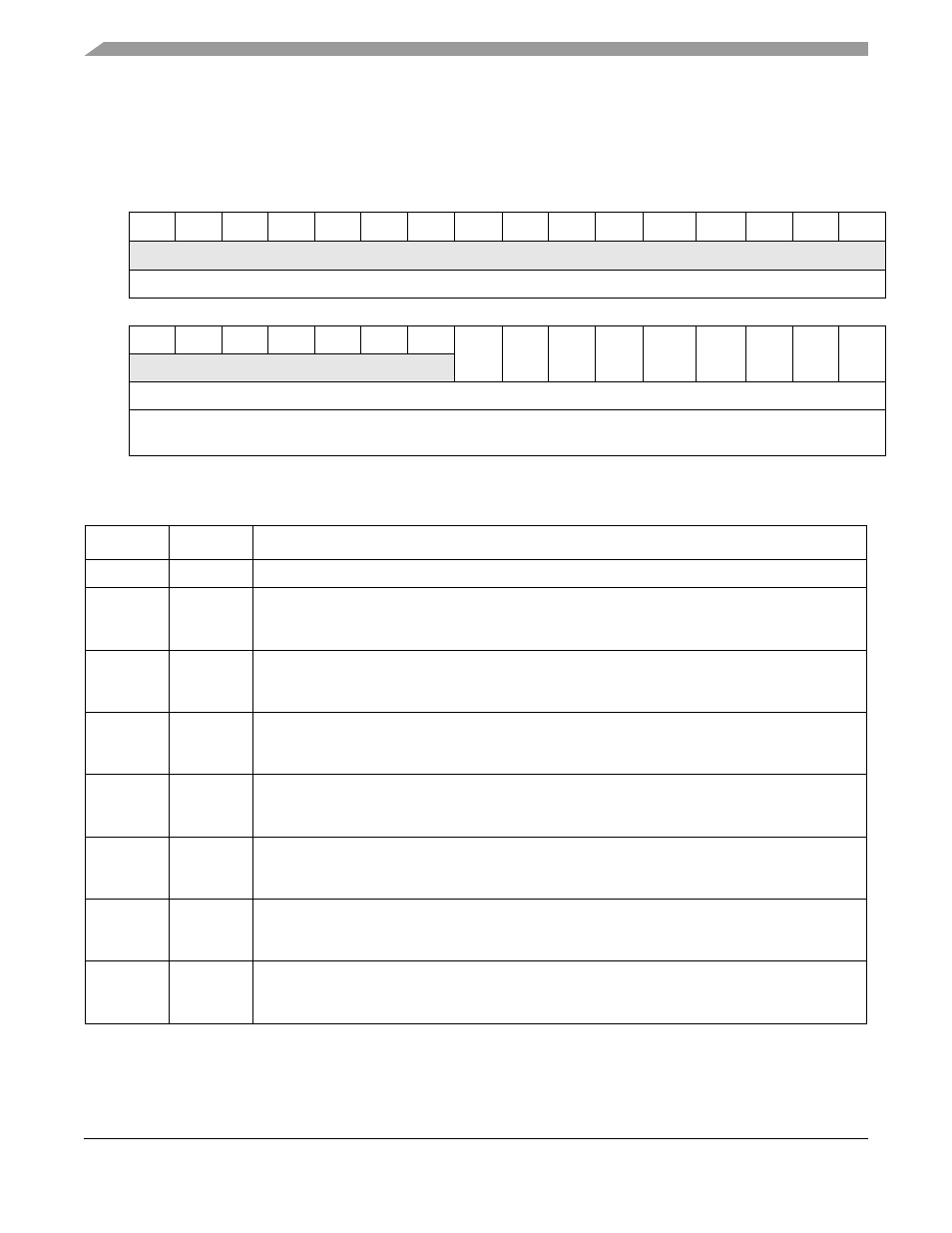

Figure 10-8. Arbiter Interrupt Mask Register (XARB_IMR)

Table 10-8. XARB_IMR Field Descriptions

Bits

Name

Description

31–9

—

Reserved, should be cleared.

8

SEAE

Slave Error Acknowledge interrupt enable.

0 The corresponding interrupt source is masked.

1 The corresponding interrupt source is enabled.

7

MME

Multiple Masters at priority 0 interrupt enable.

0 The corresponding interrupt source is masked.

1 The corresponding interrupt source is enabled.

6

TTAE

TT Address Only interrupt enable.

0 The corresponding interrupt source is masked.

1 The corresponding interrupt source is enabled.

5

TTRE

TT Reserved interrupt enable.

0 The corresponding interrupt source is masked.

1 The corresponding interrupt source is enabled.

4

ECWE

External Control Word Read/Write interrupt enable.

0 The corresponding interrupt source is masked.

1 The corresponding interrupt source is enabled.

3

TTME

TBST/TSIZ mismatch interrupt enable.

0 The corresponding interrupt source is masked.

1 The corresponding interrupt source is enabled.

2

BAE

Bus Activity Tenure Time-out interrupt enable.

0 The corresponding interrupt source is masked.

1 The corresponding interrupt source is enabled.