5 transaction termination, 5 xl bus target interface, Transaction termination -63 – Freescale Semiconductor MCF5480 User Manual

Page 547: Xl bus target interface -63

Functional Description

MCF548x Reference Manual, Rev. 3

Freescale Semiconductor

19-63

assigned by the PCI SIG Steering Committee. The current list of defined encodings are provided in

19.4.4.5

Transaction Termination

If the PCI cycle Master Aborts, the interface will return 0xFFFF FFFF as read data, but complete without

error. It will issue an interrupt to the internal interrupt controller if enabled.

For abnormal transaction termination during an XL bus-initiated transaction ( retry limit reached or target

abort), an error (TEA on XL bus) is generated. It will issue an interrupt to the MCF548x interrupt controller

if such interrupts are enabled.

Transfers that cross the 32-bit boundary (greater than 4 bytes) to a PCI nonmemory address range result

in a transfer error (TEA on XL bus).. The space is defined as nonmemory if the IO/M# configuration bit

associated with that window is programmed “0”.This type of unsupported transfer does not cause an

interrupt.

19.4.5

XL Bus Target Interface

This section discusses the MCF548x as a PCI target, and as such, the following apply:

•

The target interface can issue target abort, target retry, and target disconnect terminations.

•

The target interface supports fast back-to-back cycles.

•

No support of dual address cycles as a PCI target.

•

Target transactions are not snooped by the processor.

•

Medium device selection timing only.

•

Three 32-byte buffers enhance data throughput.

The XL bus Target Interface provides access for external PCI masters to two windows of MCF548x

address space. Target Base Address Translation Registers 0 and 1 allow the user to map PCI address hits

on MCF548x PCI Base Address Registers to areas in the internal address space. All of these registers must

be enabled for this interface to operate.

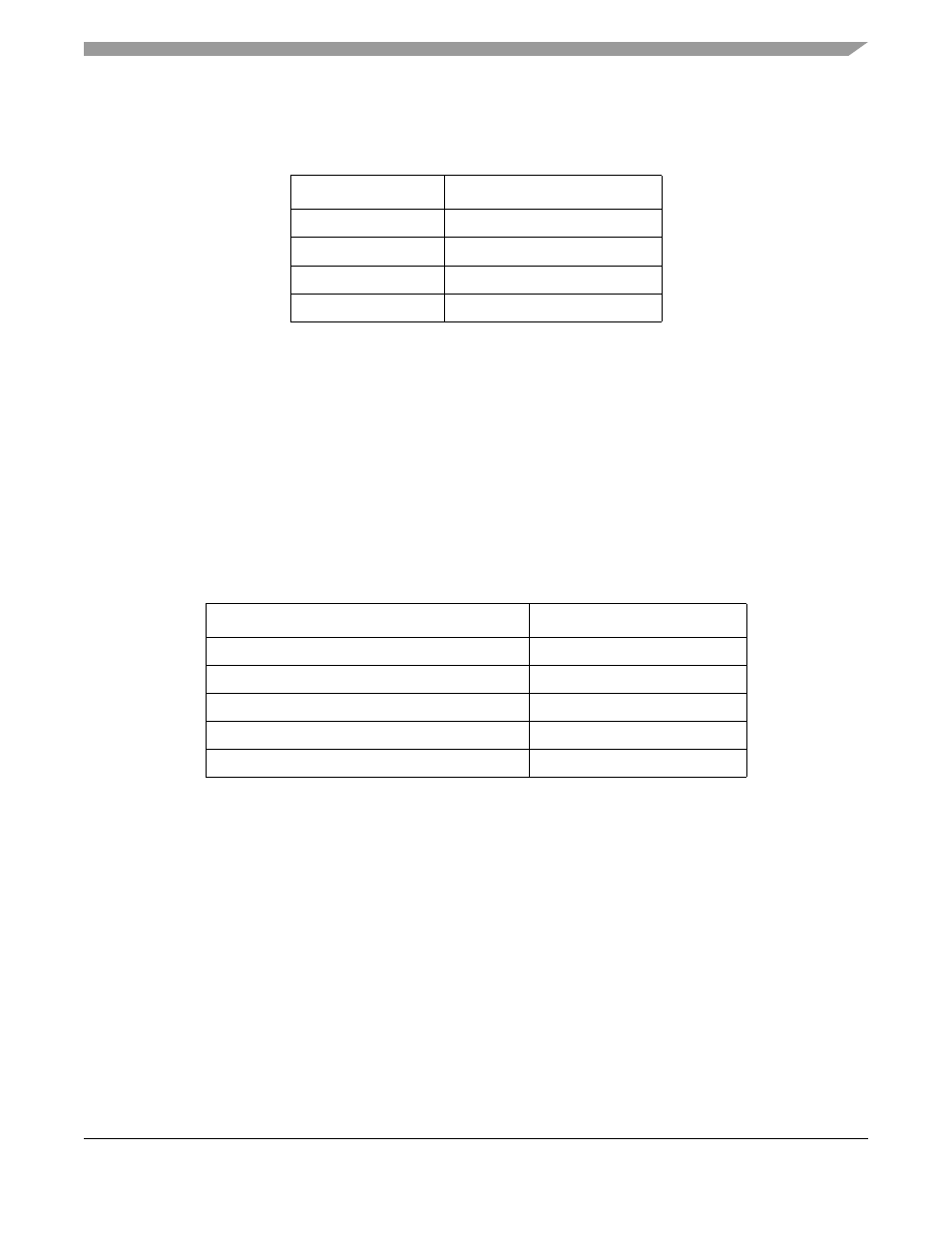

Table 19-51. Special Cycle Message Encodings

PCIAD[15:0]

Message

0x0000

SHUTDOWN

0x0001

HALT

0x0002

x86 architecture-specific

0x0003–0xFFFF

—

Table 19-52. Unsupported XL Bus Transfers

XL Bus Transaction

PCI Address Space

Burst (32-byte)

Nonmemory

> 4 byte Single Beat

Nonmemory

4 byte Single Beat at a[29:31] 001, 010, or 011

Nonmemory

3 byte Single Beat at a[29:31] 010 or 011

Nonmemory

2 byte Single Beat at a[29:31] 011

Nonmemory