10 rx fifo control register (pcirfcr) – Freescale Semiconductor MCF5480 User Manual

Page 529

Memory Map/Register Definition

MCF548x Reference Manual, Rev. 3

Freescale Semiconductor

19-45

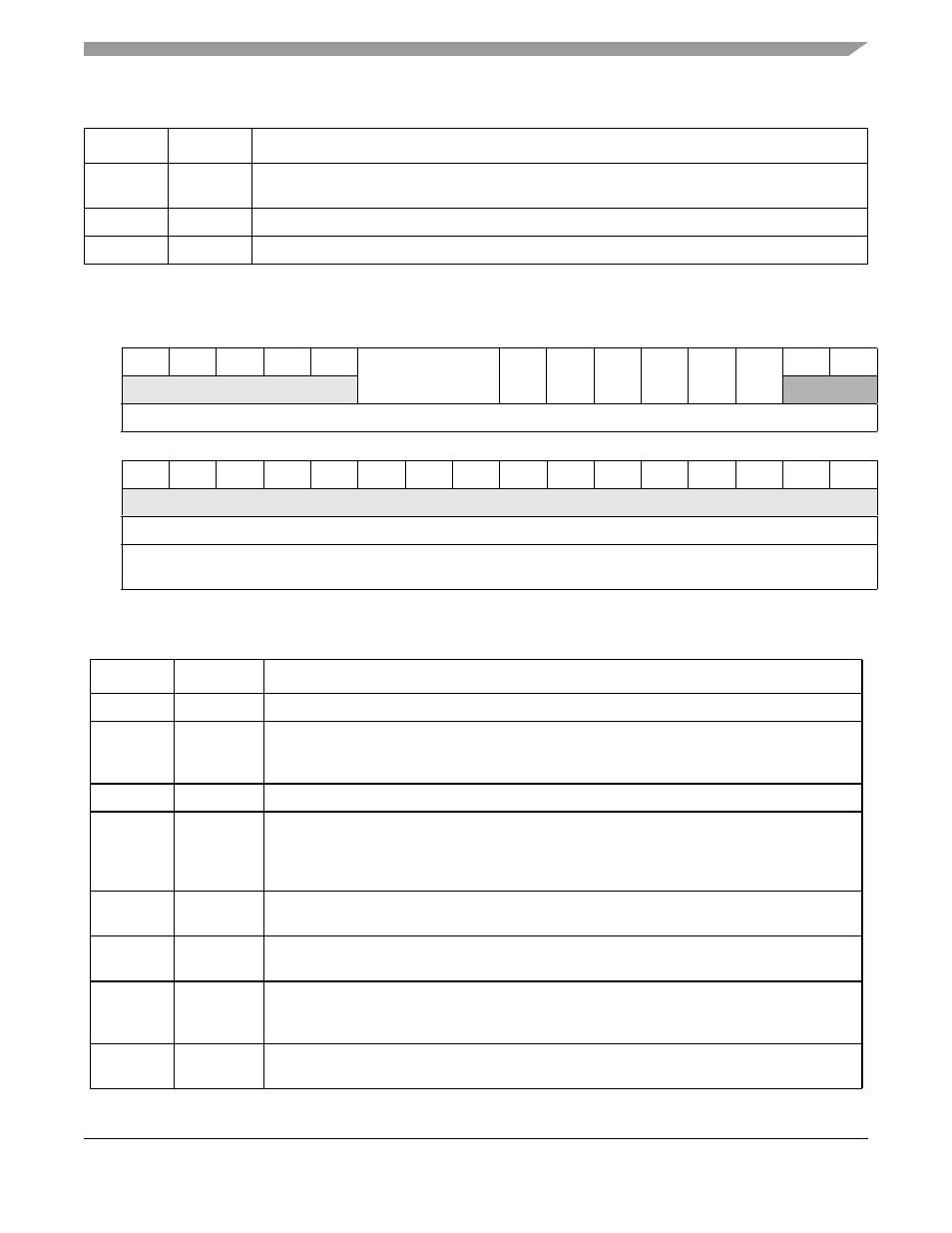

19.3.3.2.10 Rx FIFO Control Register (PCIRFCR)

17

Alarm

The FIFO is at or above the Alarm “watermark”, as set by the user according to the Alarm and

Control registers settings. This is not a sticky bit or error indication.

16

Empty

The FIFO is empty. This is not a sticky bit or error condition.

15–0

—

Reserved, should be cleared.

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

R

0

0

WFR

0

0

GR

IP_

MASK

FAE_

MASK

RXW_

MASK

UF_

MASK

OF_

MASK

TXW_

MASK

0

0

W

Reset

0

0

0

0

0

0

0

1

0

0

1

0

0

1

0

0

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

R

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

W

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Reg

Addr

MBAR + 0x84C8

Figure 19-43. Rx FIFO Control Register (PCIRFCR)

Table 19-42. PCIRFCR Field Descriptions

Bits

Name

Description

31–30

—

Reserved, should be cleared.

29

WFR

Write frame. When this bit is set, the FIFO controller assumes next data transmitted is End of

Frame (EOF).

This module does not support Framing. This bit should remain low.

28

–27

—

Reserved, should be cleared.

26–24

GR[2:0]

Granularity. Granularity bits control high “watermark” point at which FIFO negates Alarm

condition (i.e., request for data). It represents the number of bytes remaining in the FIFO.

A granularity setting of higher than (128 minus Alarm[11:0]) should be avoided because it means

the Alarm bit (and the Requestor signal) will negate as soon as it asserts.

23

IP_MASK

Illegal Pointer Mask. When this bit is set, the FIFO controller masks the Status register’s IP bit

from generating an error.

22

FAE_MASK

Frame accept error mask. When this bit is set, the FIFO controller masks the Status Register’s

FAE bit from generating an error.

21

RXW_MASK Receive wait condition mask. When this bit is set, the FIFO controller masks the Status Register’s

RXW bit from generating an error. (To help with backward compatibility, this bit is asserted at

reset.)

20

UF_MASK

Underflow mask. When this bit is set, the FIFO controller masks the Status Register’s UF bit from

generating an error.

Table 19-41. PCIRFSR Field Descriptions (Continued)

Bits

Name

Description