7 dspi rx fifo register (drfr), Dspi rx fifo register (drfr) -16 – Freescale Semiconductor MCF5480 User Manual

Page 834

MCF548x Reference Manual, Rev. 3

27-16

Freescale Semiconductor

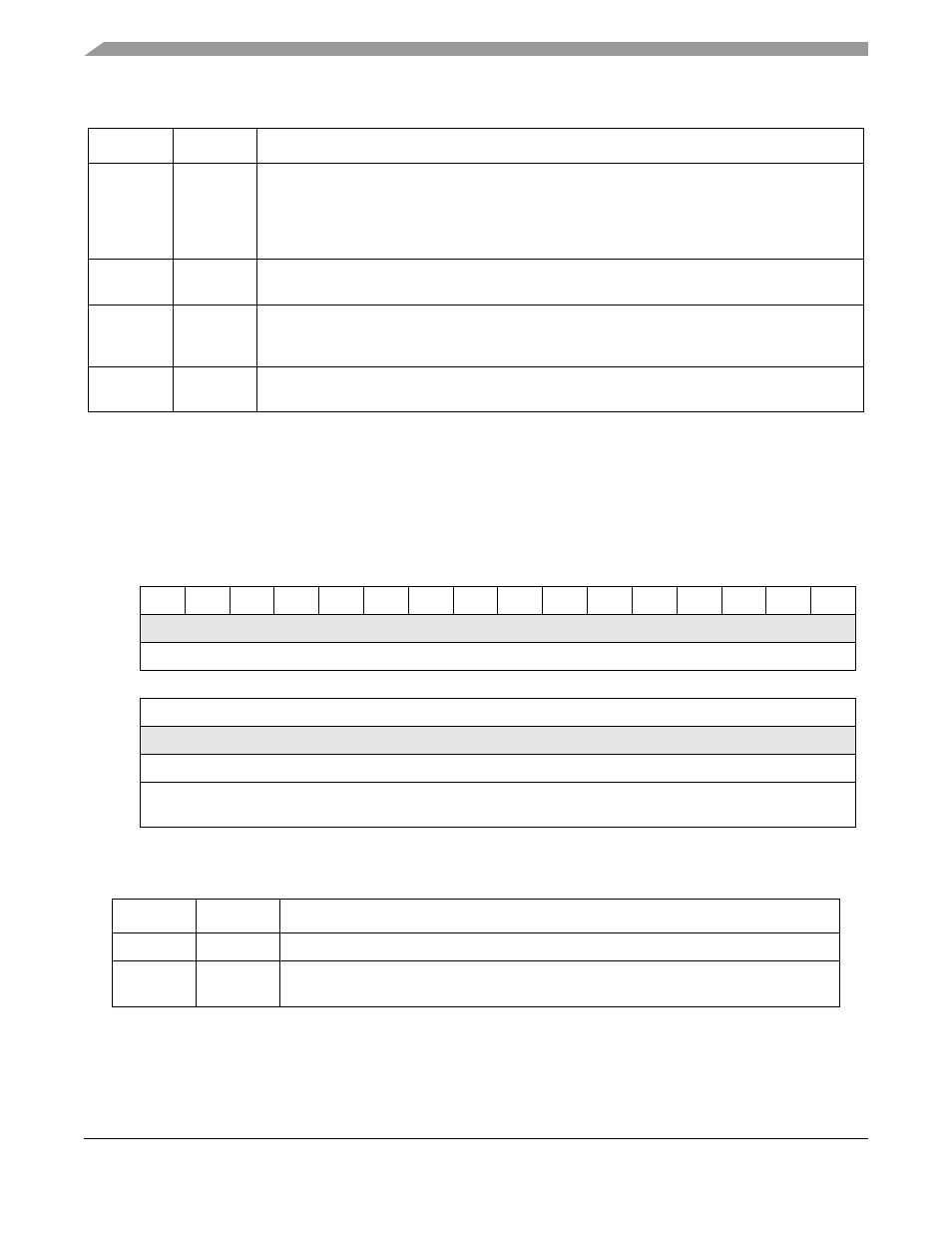

27.6.7

DSPI Rx FIFO Register (DRFR)

The DRFR provides a means to read the Rx FIFO. See

Section 27.7.2.5, “Rx FIFO Buffering Mechanism

”

for a description of the Rx FIFO operations. 8- or 16-bit read accesses to the DRFR will read from the Rx

FIFO and update the counter and pointer.

26

CTCNT

Clear SPI_TCNT. The CTCNT provides a means for host software to clear the SPI transfer counter.

The CTCNT bit clears the SPI_TCNT field in the DTCR register. The SPI_TCNT field is cleared

before transmission of the current SPI frame begins.

0 Do not clear DTCR[SPI_TCNT]

1 Clear DTCR[SPI_TCNT]

25–22,

20, 17

—

Reserved, should be cleared.

21, 19,

18, 16

CSn

DSPI chip select. The CSn bits select which

DSPICSn signals will be asserted for the transfer.

0 Negate the DSPICSn signal

1 Assert the DSPICSn signal

15–0

TXDATA

Transmit data. The TXDATA field holds SPI data to be transferred according to the associated SPI

command.

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

R

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

W

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

R

RXDATA

W

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Reg

Addr

MBAR + 0x8A38

Figure 27-8. DSPI Rx FIFO Register (DRFR)

Table 27-11. DRFR Field Descriptions

Bits

Name

Description

31–16

—

Reserved, should be cleared.

15–0

RXDATA

Received data. The RXDATA field contains the SPI data from the Rx FIFO entry pointed to

by the receive next data pointer.

Table 27-10. DTFR Field Descriptions (Continued)

Bits

Name

Description