15 psc/irda control register (pscsicrn), Psc/irda control register (pscsicrn) -23, 15 psc/irda control register (pscsicr n ) – Freescale Semiconductor MCF5480 User Manual

Page 785

Memory Map/Register Definition

MCF548x Reference Manual, Rev. 3

Freescale Semiconductor

26-23

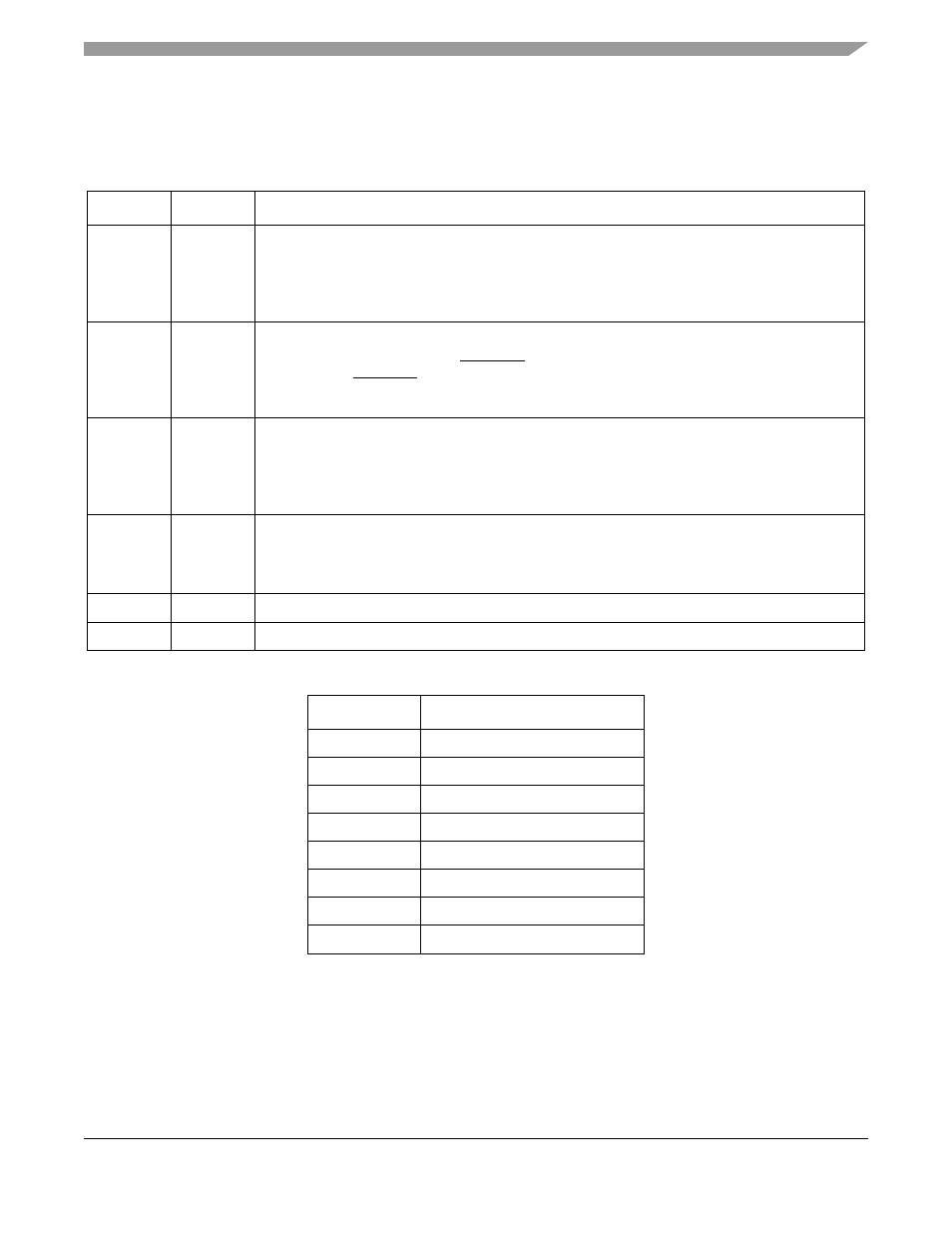

26.3.3.15 PSC/IrDA Control Register (PSCSICRn)

This register sets the main operation mode.

NOTE

When the operating mode change occurs, all receiver, transmitter, and error

statuses are reset and the receiver and transmitter are disabled.

Table 26-20. PSCSICRn Field Descriptions

Bits

Name

Descriptions

7

ACRB

This field is reserved in UART, SIR, MIR, FIR, and modem modes.

In AC97 mode, this bit signifies Cold Reset to the transceiver in PSC

0 The transceiver recovers from low power mode in AC97.

1 The transceiver stays in the current state.

This bit is included for compatibility with USART.

6

AWR

This field is reserved in UART, SIR, MIR, FIR, and modem modes.

In AC97 mode, this bit signifies Warm Reset (to the transceiver in PSC and AC97 CODEC)

0 AC97 warm reset is negated. PSCnRTS output functions normally as the AC97 frame sync.

1 Force “1” on PSCnRTS output which is used as the AC97 frame sync and the transceiver in PSC

recovers from power down mode.

5

DTS1

This field is reserved in UART, SIR, MIR, FIR, and AC97 modes.

In modem modes, this bit signifies delay of time slot 1.

0 The first bit of the first time slot of a new frame starts at the rising edge of frame sync.

1 The first bit of the first time slot of a new frame starts one bit clock cycle after the rising edge of

frame sync.

4

SHDIR

This field is reserved in UART, SIR, MIR, FIR, and AC97 modes.

In modem modes, this bit signifies Shift Direction

0 MSB first

1 LSB first

3

—

Reserved, should be cleared.

2–0

SIM

PSC/IrDA operation mode. See

Table 26-21. SIM[2:0]

SIM[2:0]

Operation Mode

000

UART

001

8 bit soft modem

010

16 bit soft modem

011

AC97

100

SIR

101

MIR

110

FIR

111

Illegal